GPP Series User Manual

194

In general it is best to use the Operation Complete Bit (bit 0) in the

standard event register to check to see if an operation/command

has completed. After executing the *OPC command, the OPC bit

will be set to 1. If a command or query is placed in the output

buffer immediately before the *OPC command is sent, the

Operation Complete Bit can be used to determine when the

information can be used. However if too many commands/queries

are executed prior to the execution of the *OPC command, the

output buffer could become saturated and the unit will stop taking

readings.

Standard Event Register

The Standard Event Register reports the following types or events:

Power on has been detected, command syntax errors, command

execution errors, self test and execution errors, query errors or if the

*OPC command is executed. Any one or more of these events will

set the standard event summary bit in the status byte register. To

set a mask for the enable register, a binary-weighted decimal

number must be written using the *ESE command.

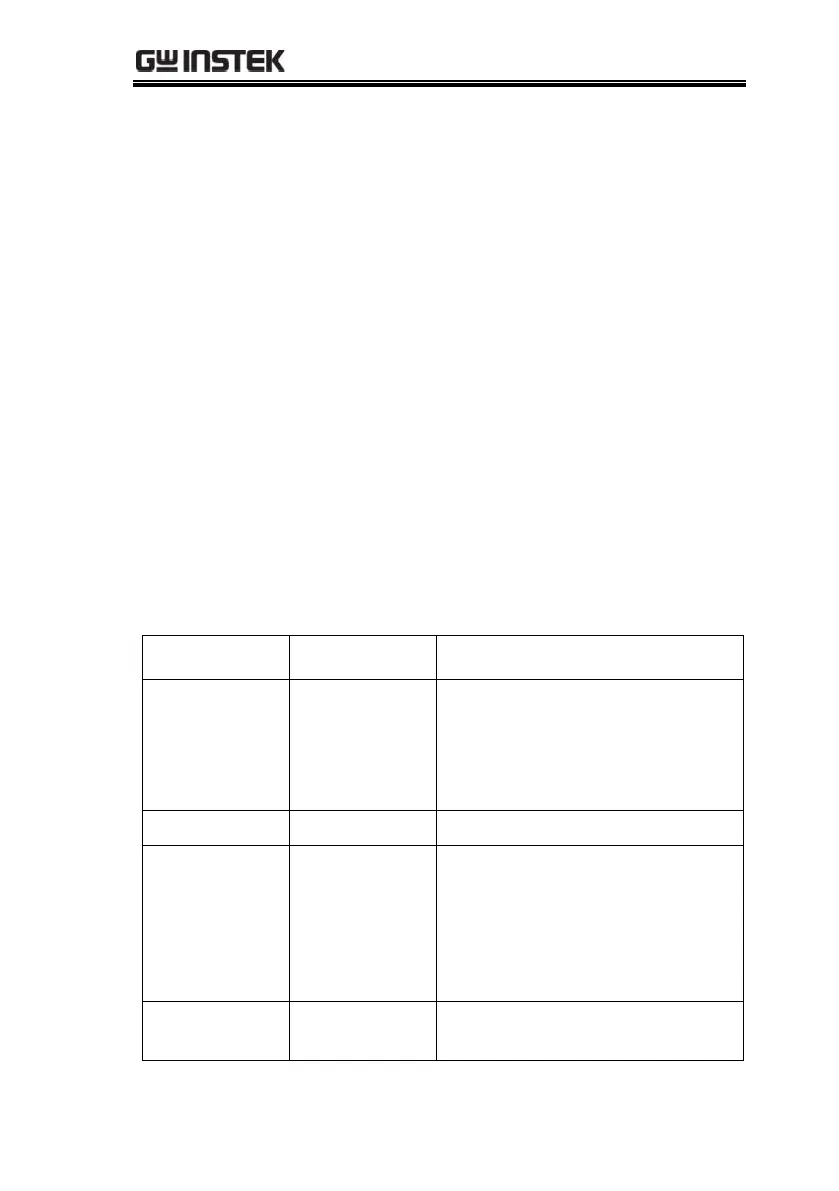

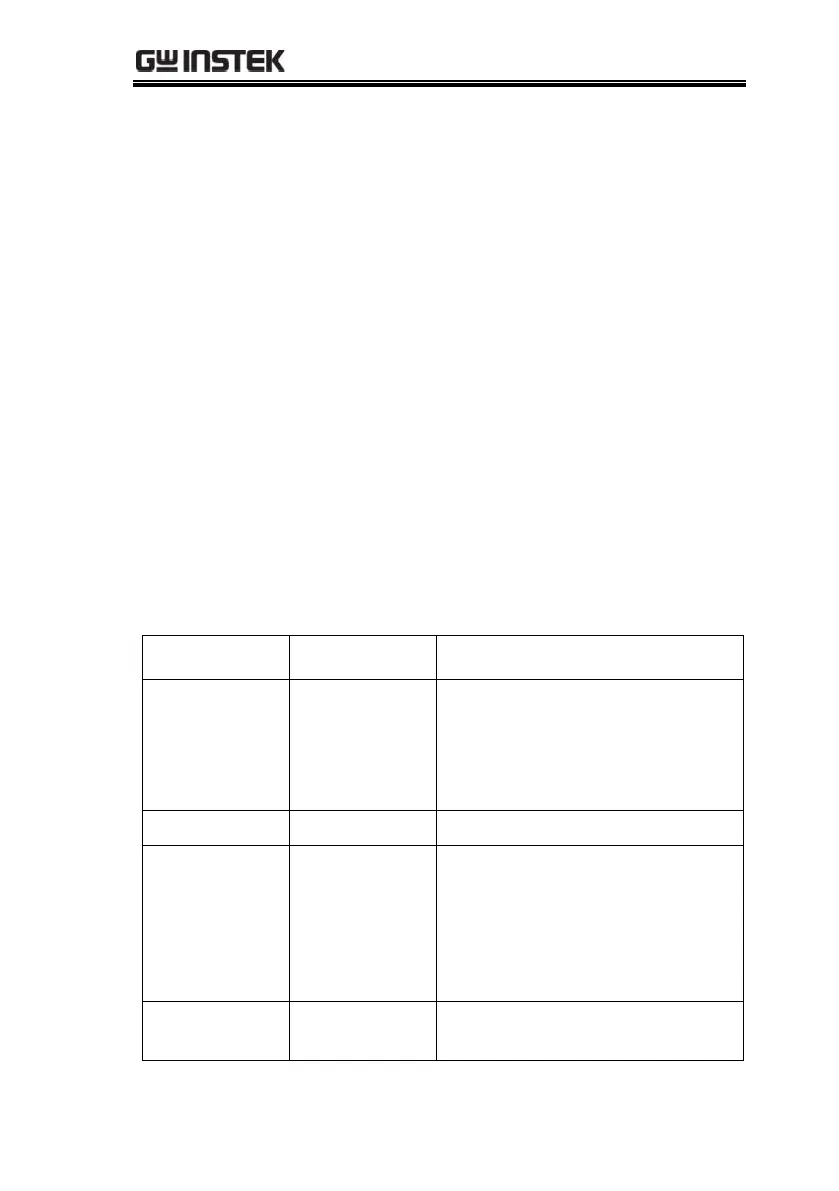

Bit Definition for the Standard Event Register

The *OPC command will set this

bit when all overlapping

operations have completed

(including the *OPC command

itself).

The instrument tried to read the

error queue when the queue was

empty or the queue was read

before a new command was given

or the input/output buffers are

full.

A self-test, calibration or other

device-specific error.

Loading...

Loading...