122

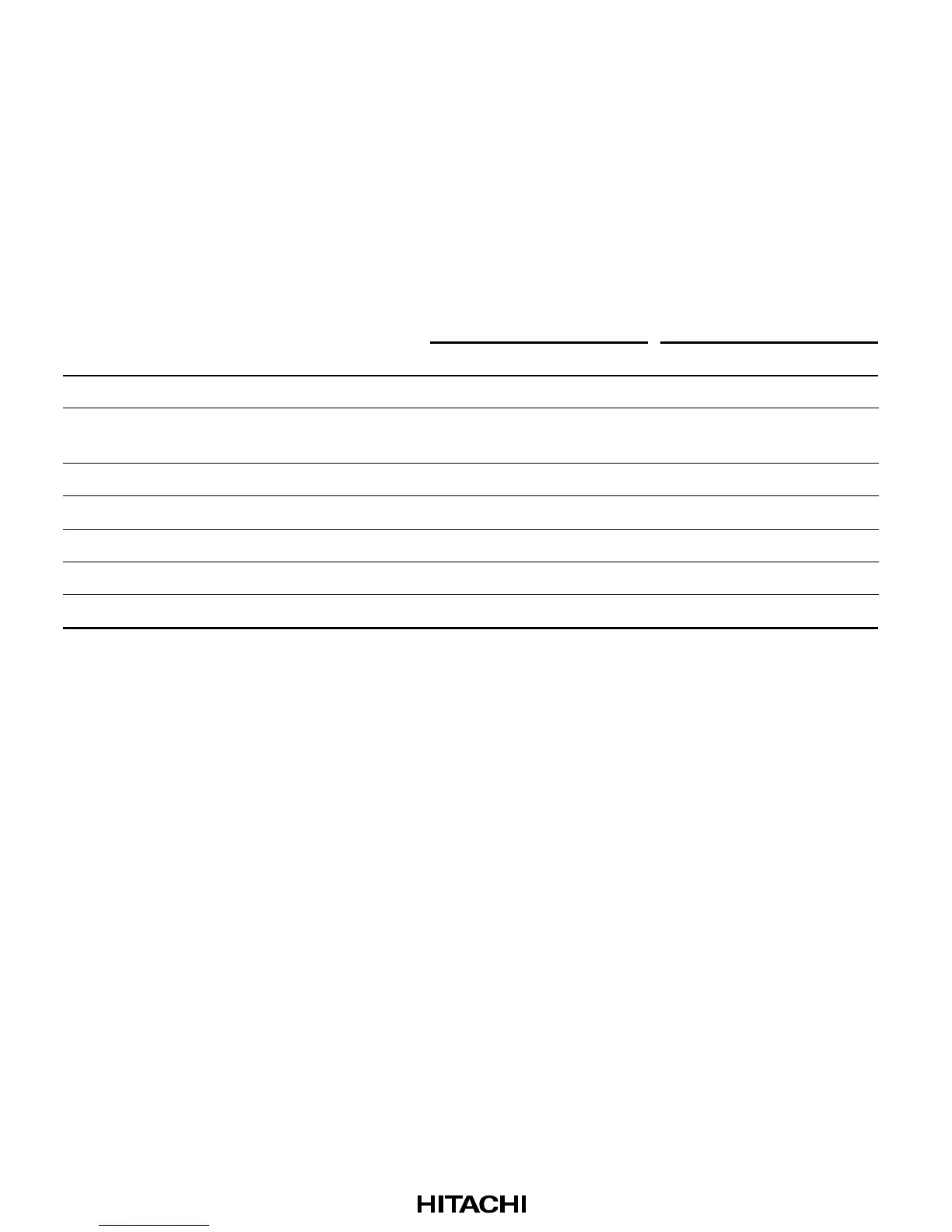

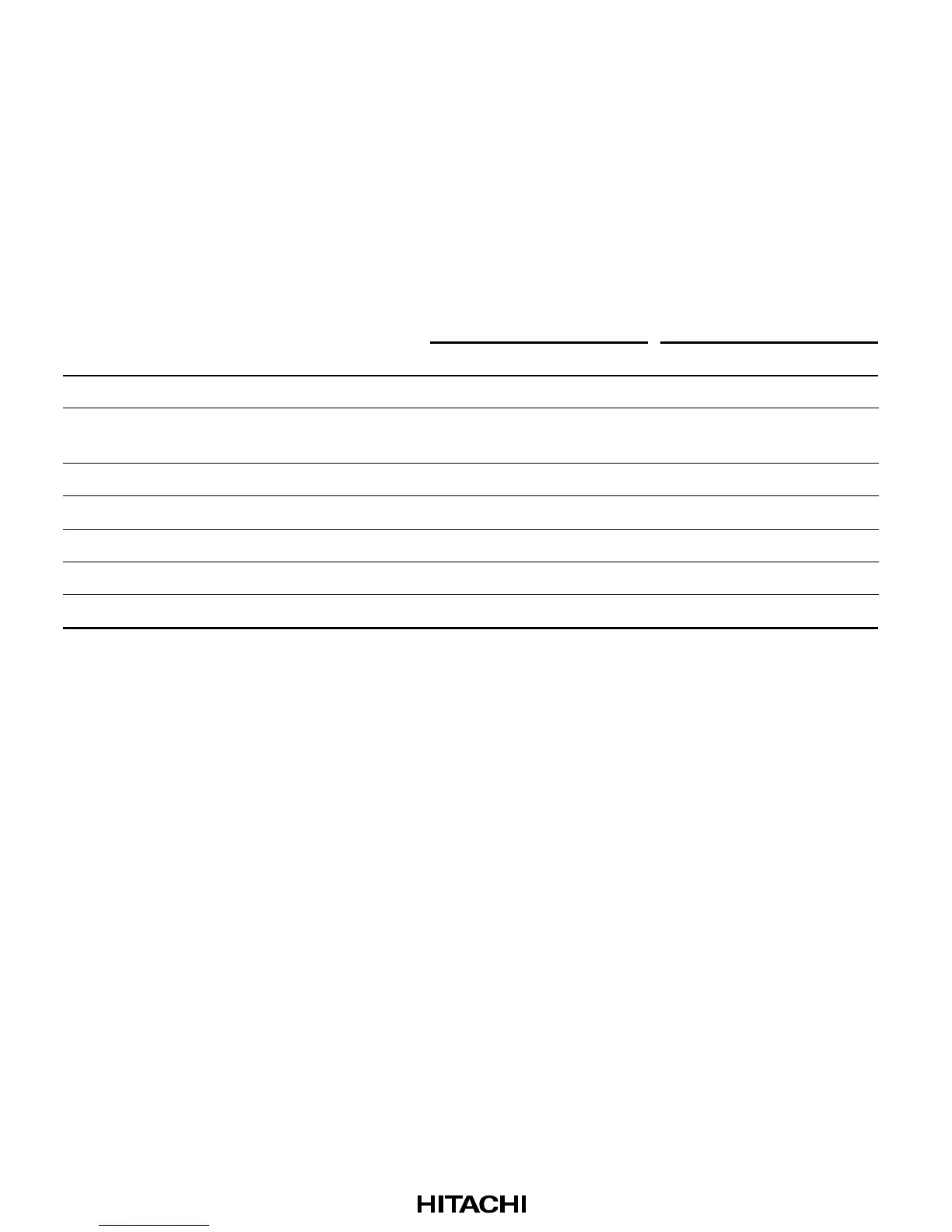

5.4.5 Interrupt Response Times

The H8S/2646 Series is capable of fast word transfer instruction to on-chip memory, and the

program area is provided in on-chip ROM and the stack area in on-chip RAM, enabling high-

speed processing.

Table 5-9 shows interrupt response times - the interval between generation of an interrupt request

and execution of the first instruction in the interrupt handling routine. The execution status

symbols used in table 5-9 are explained in table 5-10.

Table 5-9 Interrupt Response Times

Normal Mode

*5

Advanced Mode

No. Execution Status INTM1 = 0 INTM1 = 1 INTM1 = 0 INTM1 = 1

1 Interrupt priority determination

*1

33 33

2 Number of wait states until executing

instruction ends

*2

1 to

(19+2·S

I

)

1 to

(19+2·S

I

)

1 to

(19+2·S

I

)

1 to

(19+2·S

I

)

3 PC, CCR, EXR stack save 2·S

K

3·S

K

2·S

K

3·S

K

4 Vector fetch S

I

S

I

2·S

I

2·S

I

5 Instruction fetch

*3

2·S

I

2·S

I

2·S

I

2·S

I

6 Internal processing

*4

22 22

Total (using on-chip memory) 11 to 31 12 to 32 12 to 32 13 to 33

Notes: *1 Two states in case of internal interrupt.

*2 Refers to MULXS and DIVXS instructions.

*3 Prefetch after interrupt acceptance and interrupt handling routine prefetch.

*4 Internal processing after interrupt acceptance and internal processing after vector fetch.

*5 Not available in the H8S/2646 Series.

Loading...

Loading...