597

16.3 Interface to Bus Master

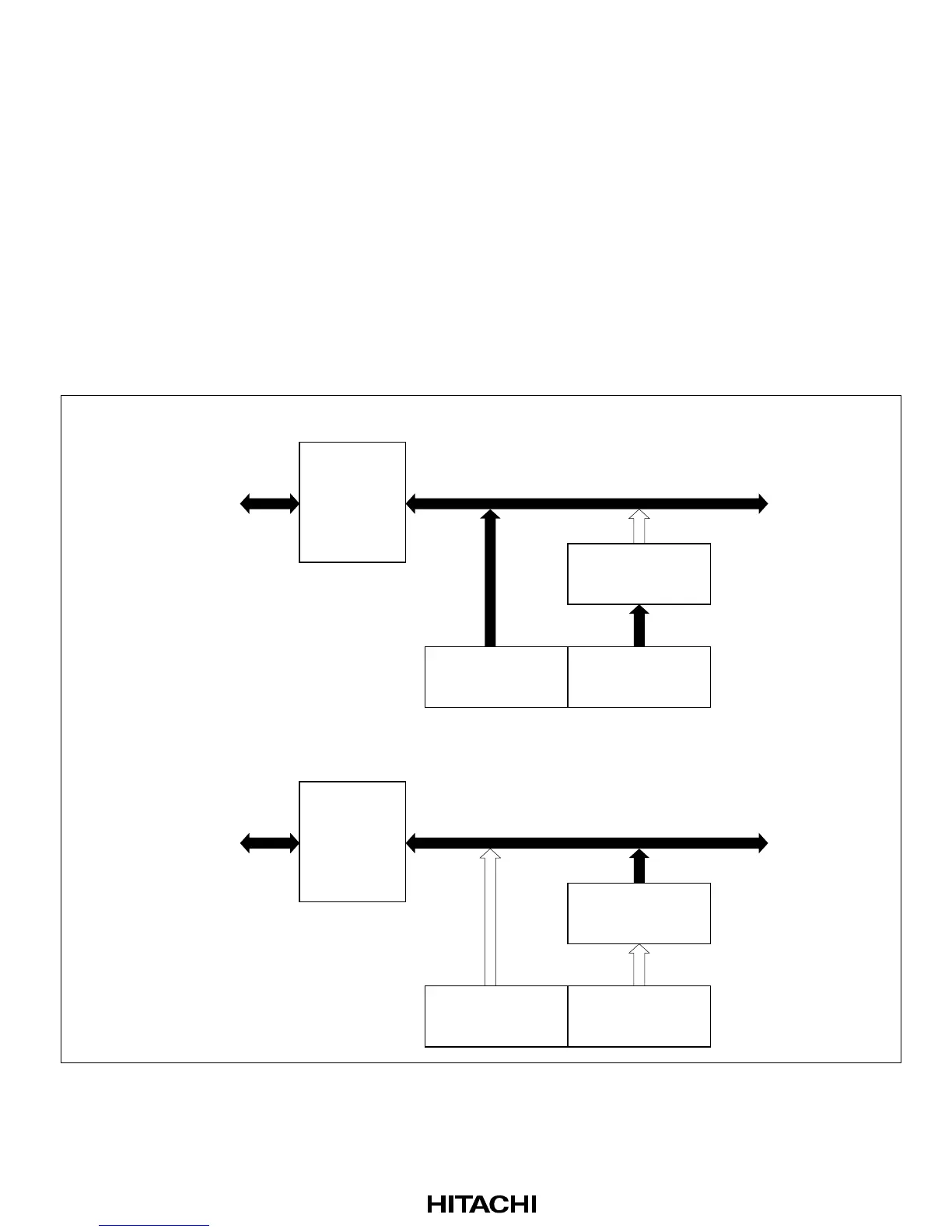

ADDRA to ADDRD are 16-bit registers, and the data bus to the bus master is 8 bits wide.

Therefore, in accesses by the bus master, the upper byte is accessed directly, but the lower byte is

accessed via a temporary register (TEMP).

A data read from ADDR is performed as follows. When the upper byte is read, the upper byte

value is transferred to the CPU and the lower byte value is transferred to TEMP. Next, when the

lower byte is read, the TEMP contents are transferred to the CPU.

When reading ADDR. always read the upper byte before the lower byte. It is possible to read only

the upper byte, but if only the lower byte is read, incorrect data may be obtained.

Figure 16-2 shows the data flow for ADDR access.

Bus master

(H'AA)

ADDRnH

(H'AA)

ADDRnL

(H'40)

Lower byte read

ADDRnH

(H'AA)

ADDRnL

(H'40)

TEMP

(H'40)

TEMP

(H'40)

(n = A to D)

(n = A to D)

Module data bus

Module data bus

Bus interface

Upper byte read

Bus master

(H'40)

Bus interface

Figure 16-2 ADDR Access Operation (Reading H'AA40)

Loading...

Loading...