34 NetVista™ Technical Information Manual

Memory connectors

15 Data bus bit 1 I/O 35 SA0 O

16 Data bus bit 14 I/O 36 SA2 O

17 Data bus bit 0 I/O 37 CS0# O

18 Data bus bit 15 I/O 38 CS1 O

19 Ground 39 Active# I

20 Key (Reserved) 40 Ground

Table 19. IDE connector-pin assignments

Pin Signal I/O Pin Signal I/O

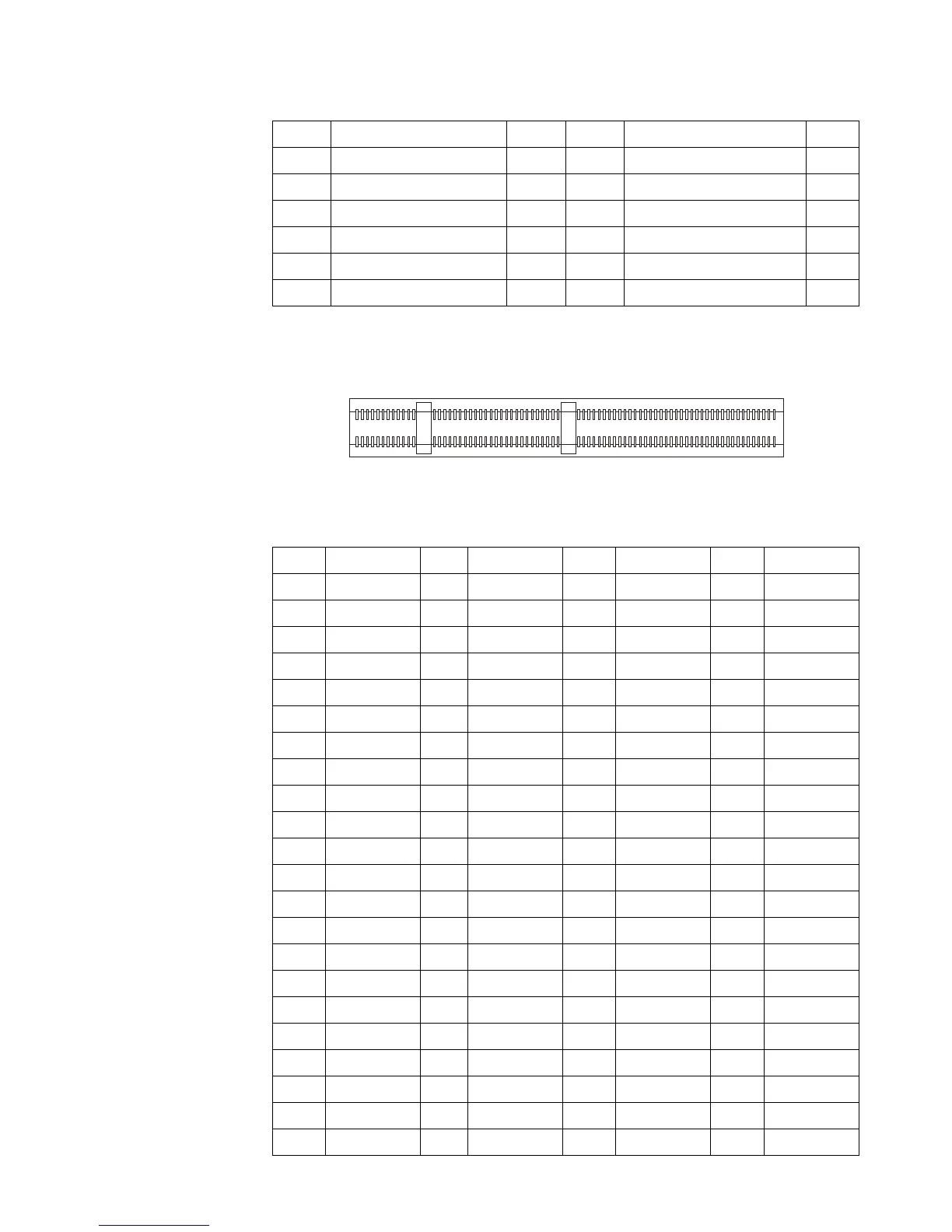

Table 20. System memory connector-pin assignments

Pin Signal Pin Signal Pin Signal Pin Signal

1 VSS 43 VSS 85 VSS 127 VSS

2 DQ0 44 DU 86 DQ32 128 CKE0

3 DQ1 45 /S2 87 DQ33 129 NC

4 DQ2 46 DQMB2 88 DQ34 130 DQMB6

5 DQ3 47 DQMB3 89 DQ35 131 DQMB7

6 VCC 48 DU 90 VCC 132 A13

7 DQ4 49 VCC 91 DQ36 133 VCC

8 DQ5 50 NC 92 DQ37 134 NC

9 DQ6 51 NC 93 DQ38 135 NC

10 DQ7 52 NC 94 DQ39 136 NC

11 DQ8 53 NC 95 DQ40 137 NC

12 VSS 54 VSS 96 VSS 138 VSS

13 DQ9 55 DQ16 97 DQ41 139 DQ48

14 DQ10 56 DQ17 98 DQ42 140 DQ49

15 DQ11 57 DQ18 99 DQ43 141 DQ50

16 DQ12 58 DQ19 100 DQ44 142 DQ51

17 DQ13 59 VCC 101 DQ45 143 VCC

18 VCC 60 DQ20 102 VCC 144 DQ52

19 DQ14 61 NC 103 DQ46 145 NC

20 DQ15 62 NC 104 DQ47 146 NC

21 NC 63 NC 105 NC 147 NC

22 NC 64 VSS 106 NC 148 VSS

1

85

84

168

Loading...

Loading...