Chapter 2. Architecture and technical overview 51

The memory-placement rules are as follows:

Plug sequence will always allow for memory mirroring (for example, no feature code needs

to be specified for memory mirroring). The highlighted (green) cells in the following tables

indicate the Active Memory Mirroring (AMM) base configuration.

DIMMs must be installed by 4x DIMMs at a time, referred to as a DIMM-quad.

DIMM-quads must be homogeneous; only DIMMs of the same feature code (FC) or

custom card identification number (CCIN) are allowed on the same quad.

Minimum requirement is two quads of identical memory (that is, the same feature

code/CCIN) per enclosure.

A DIMM-quad is the minimum installable unit for subsequent upgrades.

Although each drawer can have different capacity memory DIMMs, for maximum memory

performance, the total memory capacity on each memory controller should be equivalent.

The DIMM-quad placement rules for a single enclosure are as follows:

– Quad 1: J1A, J2A, J5A, J6A (mandatory minimum for each enclosure)

– Quad 2: J3A, J4A, J7A, J8A (mandatory minimum for each enclosure)

– Quad 3: J1B, J2B, J5B, J6B

– Quad 4: J3B, J4B, J7B, J8B

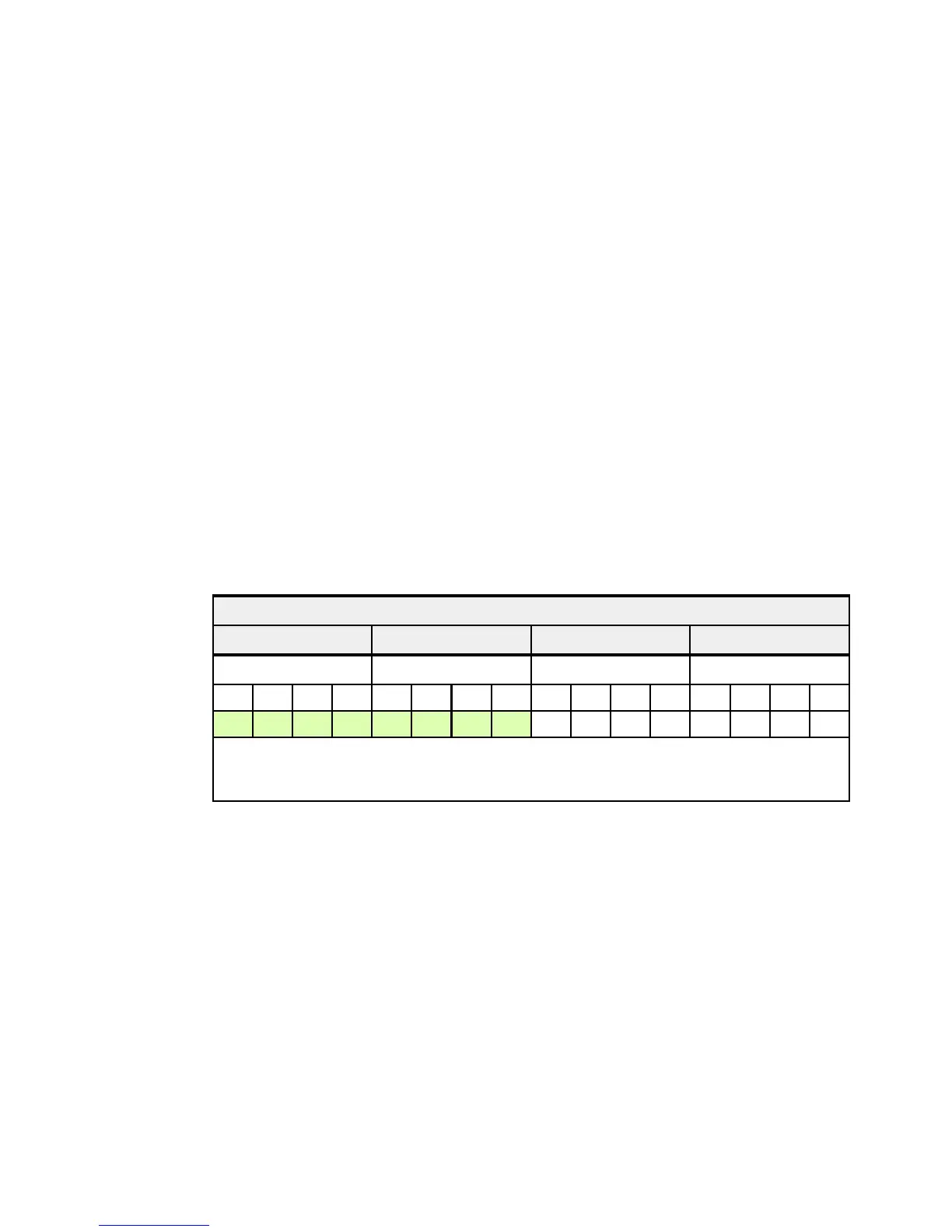

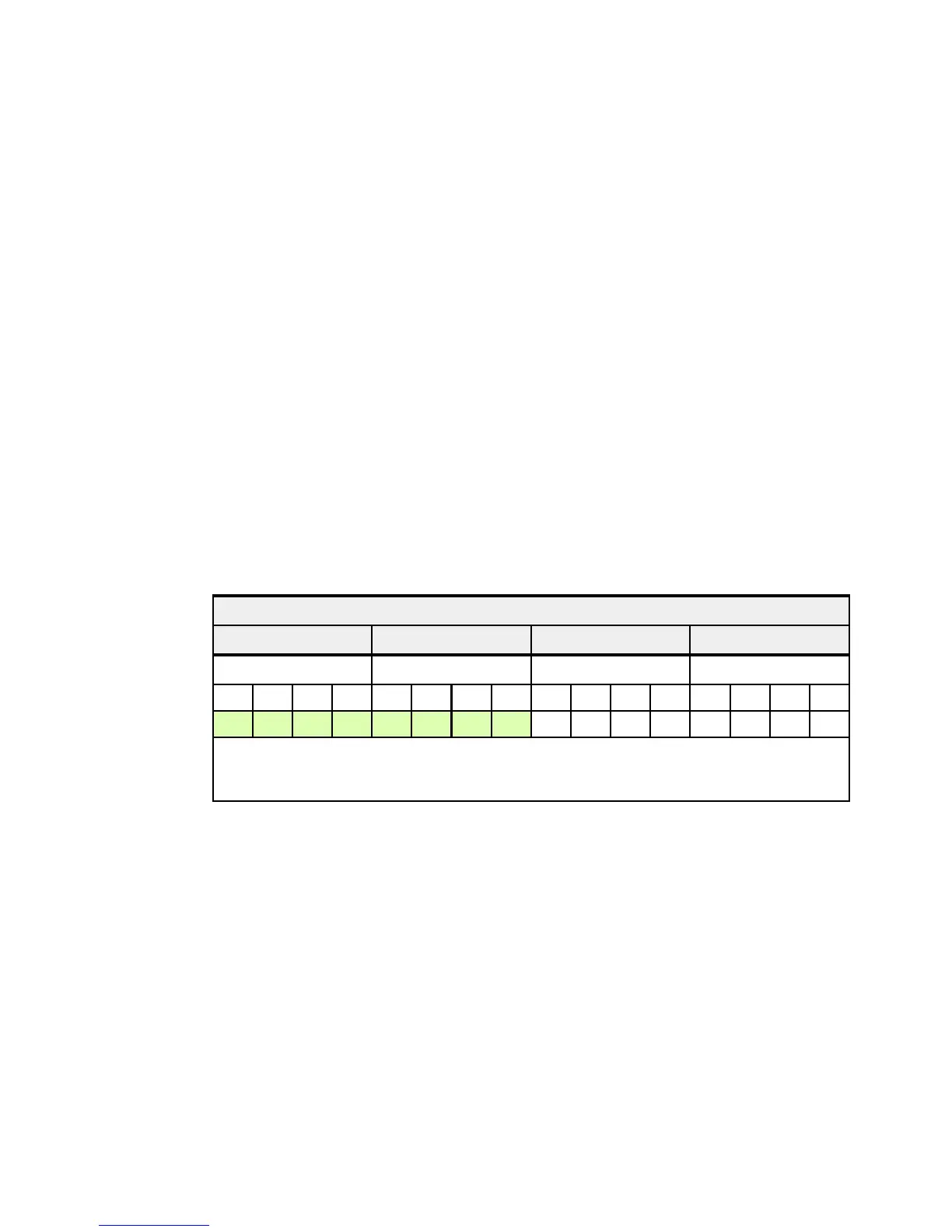

Table 2-3 shows the optimal placement of each DIMM-quad within a single enclosure system.

The enclosure

must have at least two DIMM-quads installed in slots J1A, J2A, J5A, J6A, and

J5A, J6A, J7A, and J8A, as shown with the highlighted color.

Table 2-3 Optimum DIMM-quad placement for a single enclosure system

When populating a multi-enclosure system with DIMM-quads, each enclosure must have at

least two DIMM-quads installed in slots J1A, J2A, J5A, J6A, J3AB, J4A, J7A, and J8A. After

the mandatory requirements and memory-plugging rules are followed, there is an optimal

approach to populating the systems.

Enclosure 1

CPU 1 CPU 3 CPU 4 CPU 2

Memory controller Memory controller Memory controller Memory controller

J1A J2A J3A J4A J5A J6A J7A J8A J1B J2B J3B J4B J5B J6B J7B J8B

Q1 Q1 Q2 Q2 Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4 Q3 Q3 Q4 Q4

Quads Q1 and Q2 must be identical to each other.

Note: For maximum memory performance, the total memory capacity on each memory controller

must be equivalent.

Loading...

Loading...