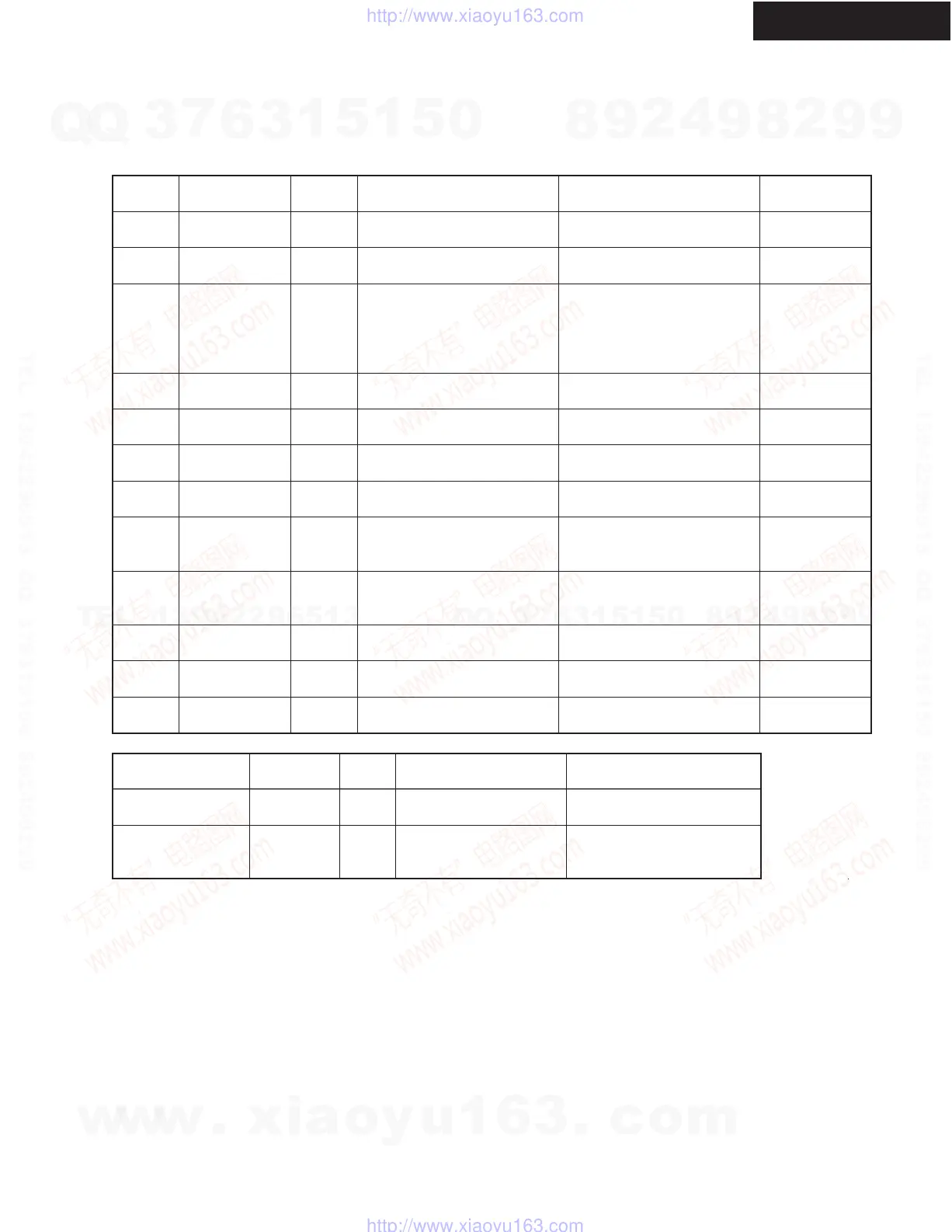

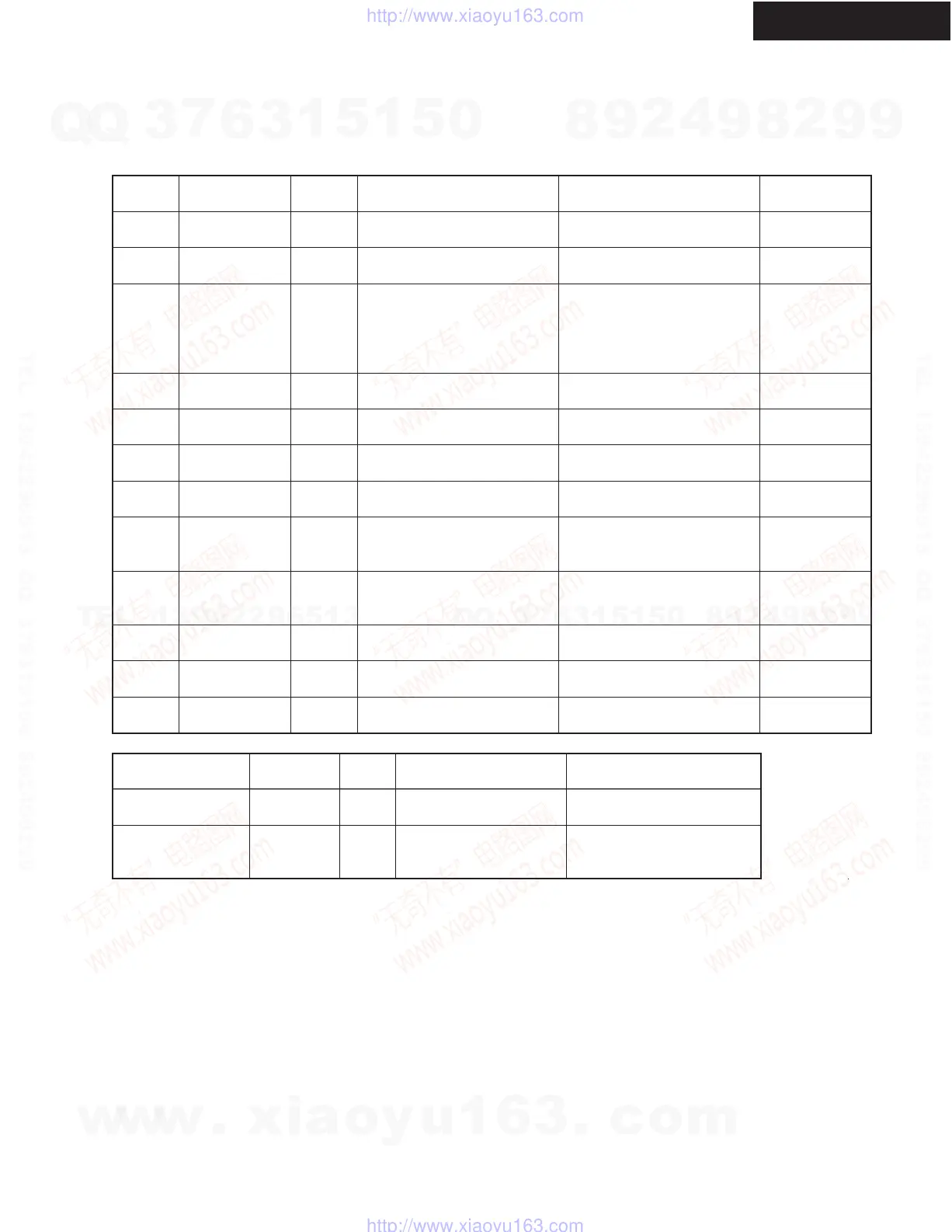

IC BLOCK DIAGRAMS AND TERMINAL DESCRIPTIONS -67

Q4 : F2628E-01 (XM Digital Transceiver)

TERMINAL DESCRIPTION(2/2)

TX-SR806/SA806

32 HSDP_DATA

S=In

M=Out

High Speed Data Port Data

Input

High Speed Data Port Data

Output

Out= 4mA, SLC

In=LVTTL S/T

34 HSDP_CLK

S=In

M=Out

High Speed Data Port Clock

Input

High Speed Data Port Clock

Output

Out= 4mA, SLC

In=LVTTL S/T

35 DT4_MODE

S=In

M=In

Enables/Disables driver on

SC_RATE and ANT_REV

(High = enable driver) This

pin was VSS on rev 3

XM/DT IC

Enables/Disables drivers on

MUTE and ANT_REV (High

= enable drivers) This pin

was VSS on rev 3 XM/DT IC

In=LVTTL S/T

36 HSDP_EN#

S=In

M=Out

High Speed Data Port Enable

Input (Active low)

High Speed Data Port Enable

Output (Active low)

Out= 4mA, SLC

In=LVTTL S/T

37 I2S_DATA

S=In

M=Out

I2S Digital Audio Port Data In

I2S Digital Audio Port Data

Out

Out= 4mA, SLC

In=LVTTL S/T

39 I2S_SCLK

S=In

M=Out

I2S Digital Audio Port Bit

Clock In

I2S Digital Audio Port Bit

Clock Out

Out= 4mA, SLC

In=LVTTL S/T

41 I2S_LRCLK

S=In

M=Out

I2S Digital Audio Port

Left/Right Clock In

I2S Digital Audio Port

Left/Right Clock Out

Out= 4mA, SLC

In=LVTTL S/T

43 I2S_OCLK

S=In

M=Out

I2S Digital Audio Port

Oversample Clock

(not used, leave unconnected)

I2S Digital Audio Port

Oversample Clock Out

Out= 4mA, SLC

44 MUTE

S=n/u

M=Out

Not used in Slave mode, leave

unconnected

Provides a mechanism for

muting the audio during an

I2S rate change (High=mute)

Out= 4mA, SLC

45 SAII_CLK

S=Out

M=In

SAII Port Clock Output SAII Port Clock Input

Out= 4mA, SLC

In=LVTTL S/T

47 SAII_DATA

S=Out

M=In

SAII Port Data Output SAII Port Data Input

Out= 4mA, SLC

In=LVTTL S/T

48 SAII_REQ

S=In

M=Out

SAII Port Request Input SAII Port Request Output

Out= 4mA, SLC

In=LVTTL S/T

Pin No.

Pin Name Type

Function

in Slave Mode

Function

in Master Mode

4, 8, 17, 20,

27, 33, 40, 46

VDD PWR +3.3V Supply Voltage +3.3V Supply Voltage

2, 10, 16, 21,

24, 25, 31, 38,

42

VSS GND Digital Ground Digital Ground

Pin No.

Pin Name

Direction Function in Slave Mode Function in Master Mode

Notes

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com

Loading...

Loading...