176 21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

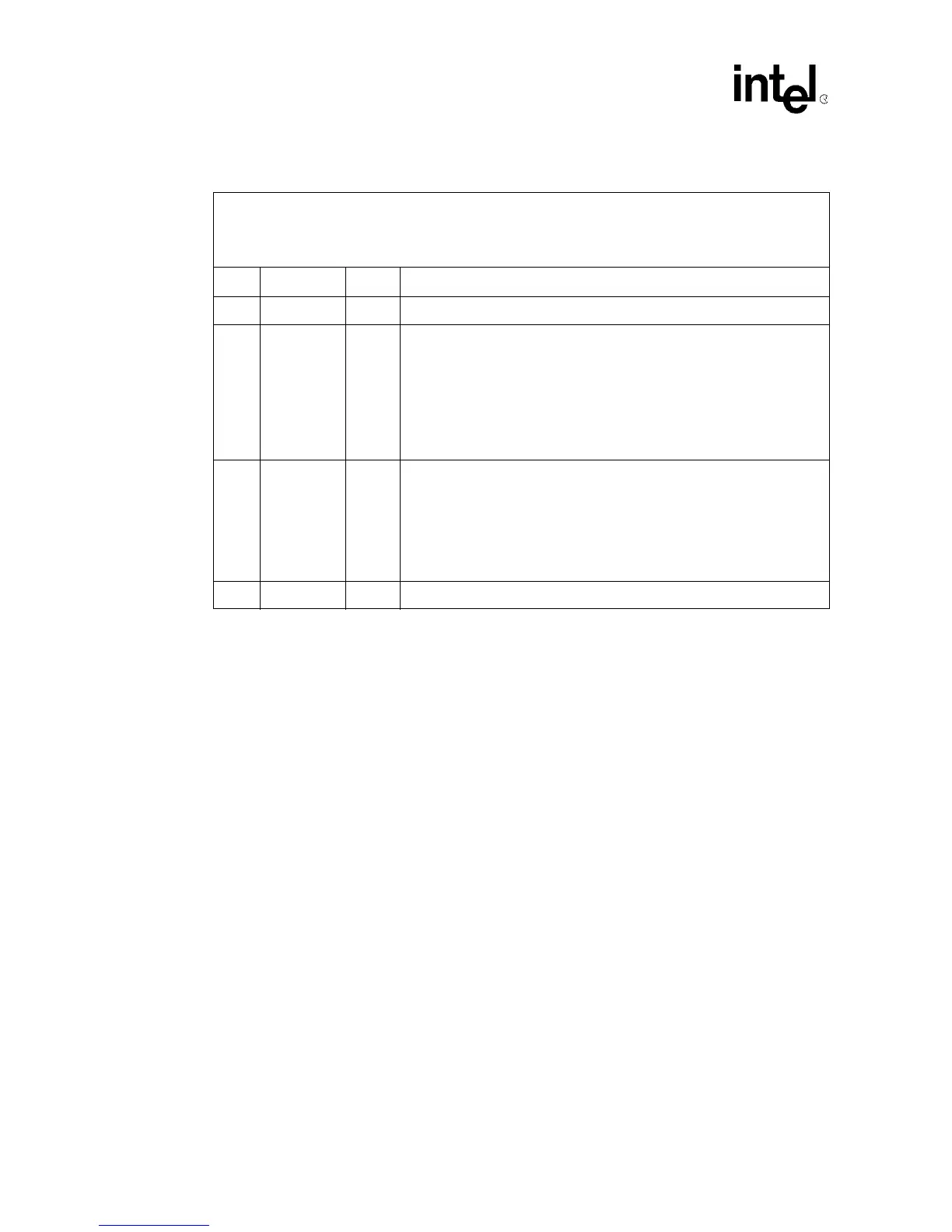

Table 108. Primary Expansion ROM Setup Register

This register may be preloaded by serial ROM or programmed by the local processor before host

configuration.

• Primary byte offset: C3:C0h

• Secondary byte offset: C3:C0h

Bit Name R/W Description

11:0 Reserved R Reserved. Read only as 0.

23:12 Size R/(WS)

These bits specify the size of the address range requested by the Primary

Expansion ROM Base Address register.

• When a bit is 1, the corresponding bit in the Primary Expansion ROM

Base Address register functions as a readable and writable bit.

• When a bit is 0, the corresponding bit in the Primary Expansion ROM

Base Address register functions as a read

-only bit that always returns

zero when read.

• Reset value is 0 (disabled).

24 BAR_Enable R/(WS)

The location of this bit in the preload sequence, as listed in “Serial Preload

Sequence” on page 16-180.

• When 0, the

Primary Expansion ROM BAR is disabled and reads

as 0.

• When 1, the

Primary Expansion ROM BAR is enabled, with size

specified by this setup register.

• Reset value is 0

31:25 Reserved R Reserved. Returns 0 when read.

Loading...

Loading...