21555 Non-Transparent PCI-to-PCI Bridge User Manual 189

List of Registers

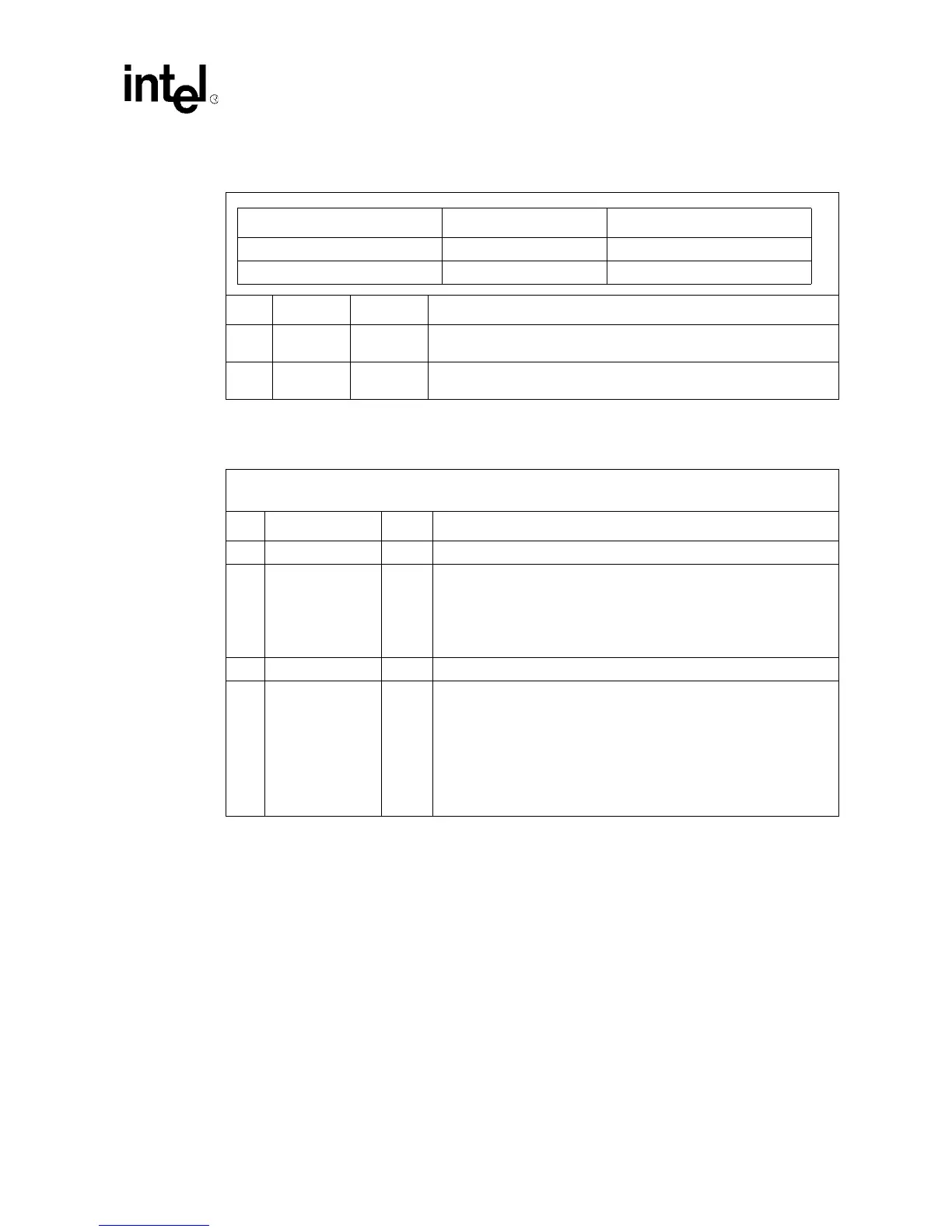

Table 124. CompactPCI Hot-Swap Capability Identifier and Next Pointer Register

Bit Name R/W Description

7:0 HS ECP ID R

Enhanced capabilities ID. Reads only as 06h to indicate that these are

CompactPCI Hot

-Swap registers.

7:0

HS NXT

PTR

R

Pointer to next set of ECP registers. Reads only as 0 to indicate that

these are the last ECP registers in this list.

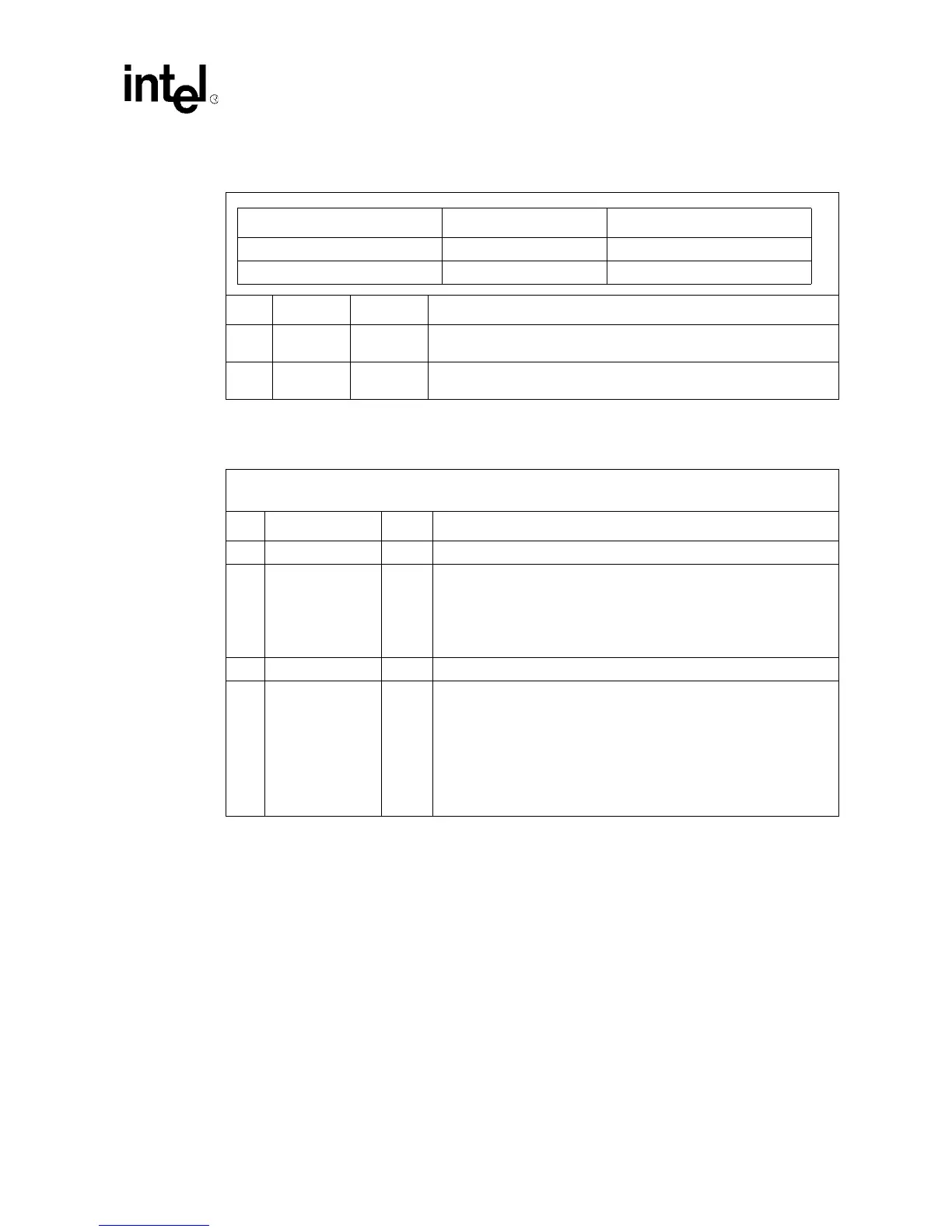

Table 125. CompactPCI Hot-Swap Control Register (Sheet 1 of 2)

• Primary byte offset: EF:EEh

• Secondary byte offset: EF:EEh

Bit Name R/W Description

0 Reserved R Reserved. Read only as 0.

1 ENUM_MASK R/W

ENUM# Interrupt Mask.

• When 0, the 21555 asserts p_enum_l when an insertion or removal

event occurs.

• When 1, the 21555 does not assert p_enum_l.

• Reset value is 0

2 Reserved R Reserved. Read only as 0.

3 LED On/Off (LOO) R/W

LED On/Off (LOO) Control. Allows software control of the l_stat pin and

therefore the state of the LED.

• When 0, the 21555 tristates l_stat. When REM STAT is low, the

LED is off when the ejector handle is closed and on when the

ejector handle is open. When REM STAT is high, l_stat is not

tristated but continues to be driven by the 21555 (LED is off).

• When 1, the 21555 drives l_stat high and the LED is forced on.

• Reset value is 0

Offsets HS ECP ID HS Next Pointer

Primary byte ECh EDh

Secondary byte ECh EDh

Loading...

Loading...