Intel® 460GX Chipset Software Developer’s Manual 11-5

LPC/FWH Interface Configuration

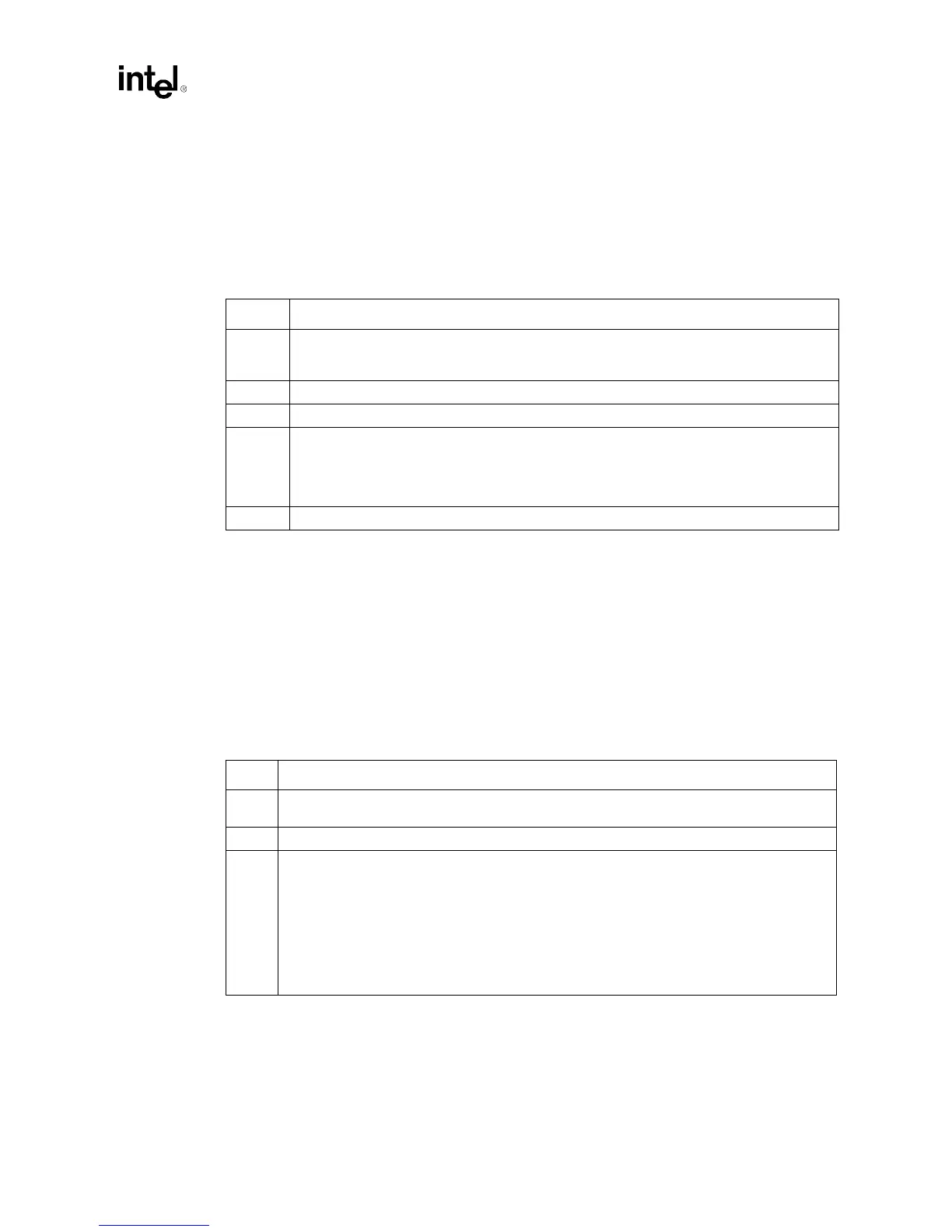

11.1.11 BIOSEN–BIOS Enable Register (FUNCTION 0)

Address Offset: 4E-4Fh

Default Value: 07C1h

Attribute: Read/Write

This register is used to implement protections to writes to firmware (BIOS) ranges.

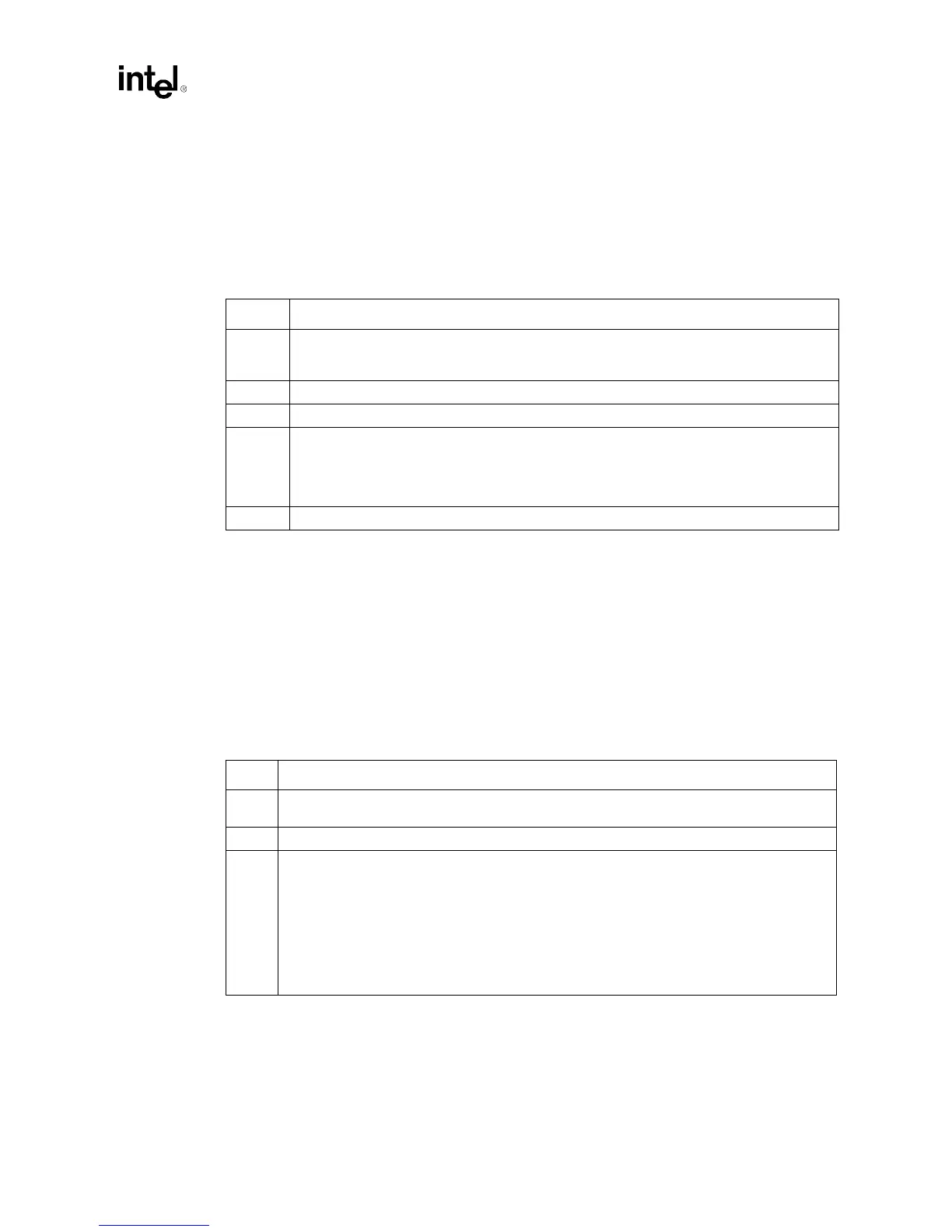

11.1.12 PIRQRC[A:D]–PIRQx Route Control Registers (Function 0)

Address Offset: 60h (PIRQRCA#)–63h (PIRQRCD#)

Default Value: 80h

Attribute: R/W

These registers control the routing of the PIRQ[A:D]# signals to the IRQ inputs of the interrupt

controller. Each PIRQx# can be independently routed to any one of 11 interrupts. All four PIRQx#

lines can be routed to the same IRQx input. Note that the IRQ that is selected through bits [3:0]

must be set to level sensitive mode in the corresponding ELCR Register. When a PIRQ signal is

routed to an interrupt controller IRQ, the IFB masks the corresponding IRQ signal.

Bit Description

15 BLE - BIOS Lock Enable: When the bit is a “1”, setting BIOS_WEN bit will cause SMIs. When this

bit is a “0”, setting BIOS_WEN will not cause SMIs. Once set, this bit can only be cleared by a

PCIRST#.

14:11 Reserved.

10:3 Reserved. Software must preserve these register values.

2 BIOS_WEN - BIOS Write Enable. When this bit is set to a “1”, writes to firmware (BIOS) ranges

are allowed. When this bit is a “0”, writes to firmware (BIOS) ranges are not allowed and write

cycles will be master-aborted on PCI. There is no protection on writes to FWH register space.

When this bit is written from a “0” to a “1”, and bit 15 (BIOS Lock Enable) is set, an SMI# is

generated.

1:0 Reserved. Software must preserve these register values.

Bit Description

7 Interrupt Routing Enable. When this bit is a “0”, the corresponding PIRQ is routed to one of the

compatibility mode interrupts specified in bits[3:0]. When this bit is a “1”, the PIRQ is not routed.

6:4 Reserved.

3:0 Interrupt Routing. When bit 7=0, this field selects the routing of the PIRQx to one of the interrupt

controller interrupt inputs.

Bits[3:0]

0000

0001

0010

0011

0100

0101

IRQ Routing

Reserved

Reserved

Reserved

IRQ3

IRW4

IRQ5

Bits[3:0]

0110

0111

1000

1001

1010

IRQ Routing

IRQ6

IRQ7

Reserved

IRQ9

IRQ10

Bits[3:0]

1011

1100

1101

1110

1111

IRQ Routing

IRQ11

IRQ12

Reserved

IRQ14

IRQ15

Loading...

Loading...