Universal Serial Bus (USB) Configuration

13-6 Intel® 460GX Chipset Software Developer’s Manual

13.2.13 INTPN–Interrupt Pin (Function 2)

Address Offset: 3Dh

Default Value: 04h

Attribute: Read only

This register indicates which PCI interrupt pin is used for the USB module interrupt. The USB

interrupt is internally ORed to the interrupt controller with the PIRQD# signal.

13.2.14 Miscellaneous Control (Function 2)

Address Offset: 6A-6Bh

Default Value: 0000h

Attribute: Read/Write

13.2.15 SBRNUM–Serial Bus Release Number (Function 2)

Address Offset: 60h

Default Value: 10h

Attribute: Read only

This register contains the release of the USB Specification with which this USB Host Controller

module is compliant.

13.2.16 LEGSUP–Legacy Support Register (Function 2)

PCI Address Offset: C0-C1h

Default: 2000h

Attribute: Read/Write Clear

This register provides control and status capability for the legacy keyboard and mouse Functions.

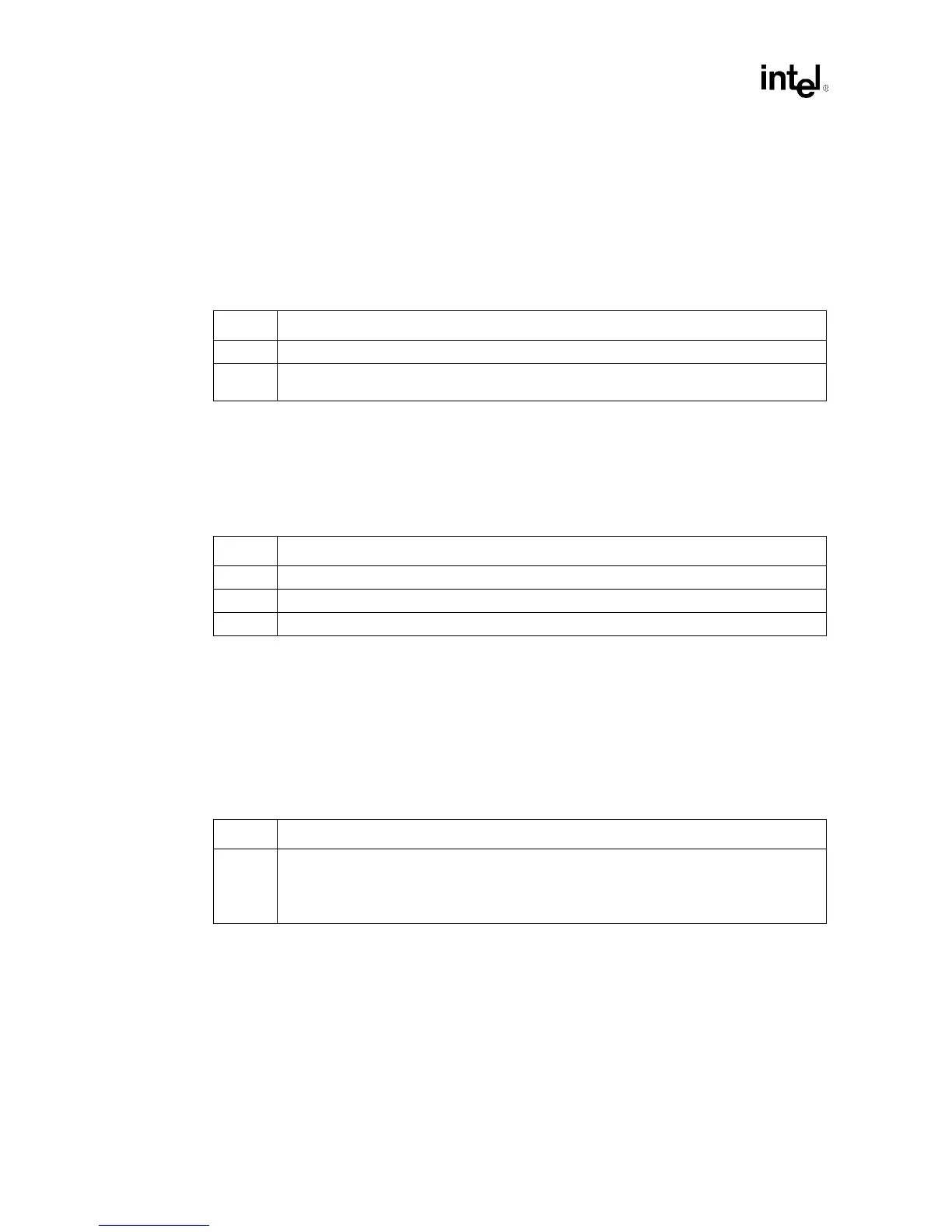

Bit Description

7:3 Reserved.

2:0 Serial Bus Module Interrupt Routing. The value of 04h in Function 2 indicates that the IFB will

drive PIRQD# as its interrupt line for the USB controller.

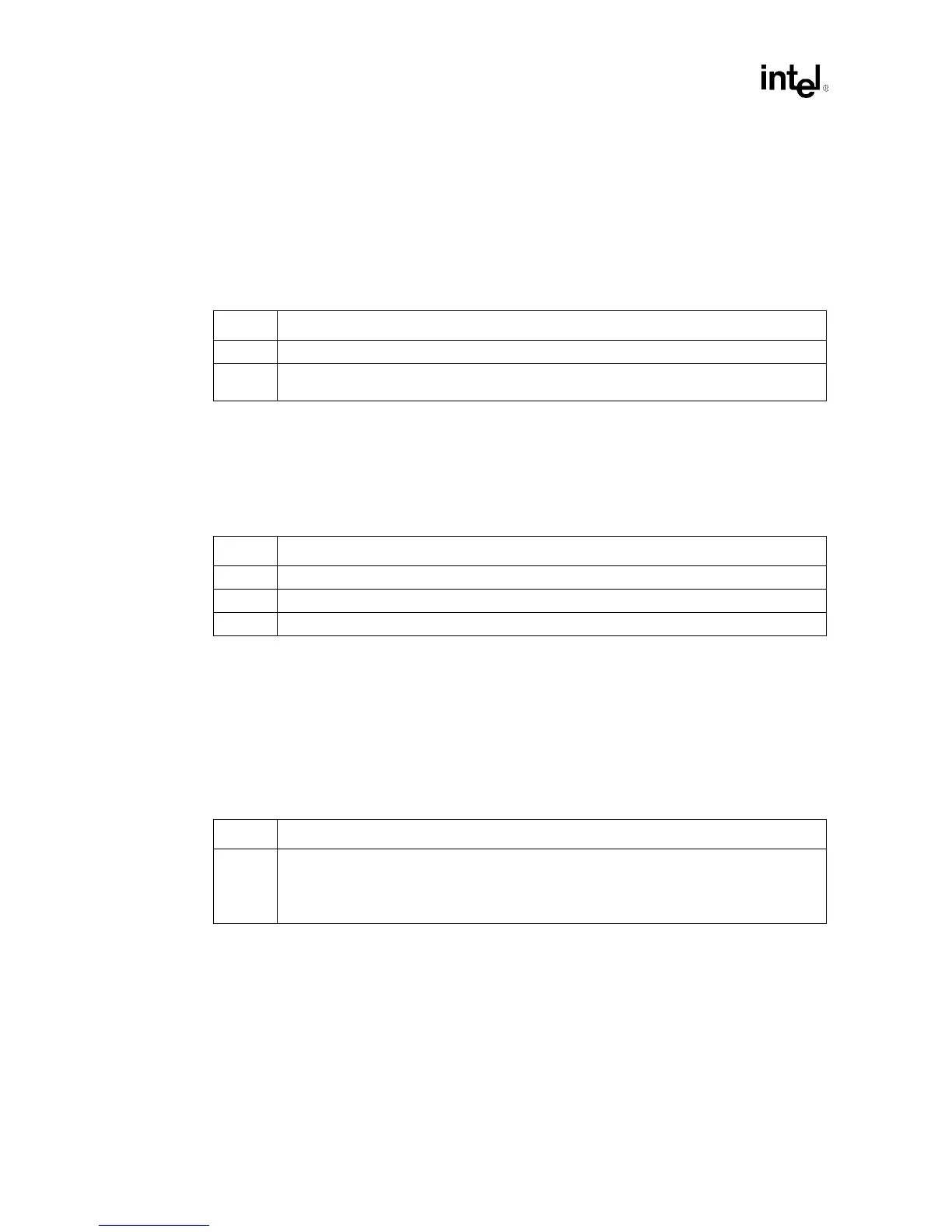

Bit Description

15:2 Reserved.

1 Low Speed PreSOF Disable. This bit should be set to ‘1’ to disable.

0 Reserved.

Bit Description

7:0 Serial Bus Specification Release Number. All other combinations are reserved.

Bits[7:0] Release Number

00h Pre-release 1.0

10h Release 1.0

Loading...

Loading...