LPC/FWH Interface Configuration

11-14 Intel® 460GX Chipset Software Developer’s Manual

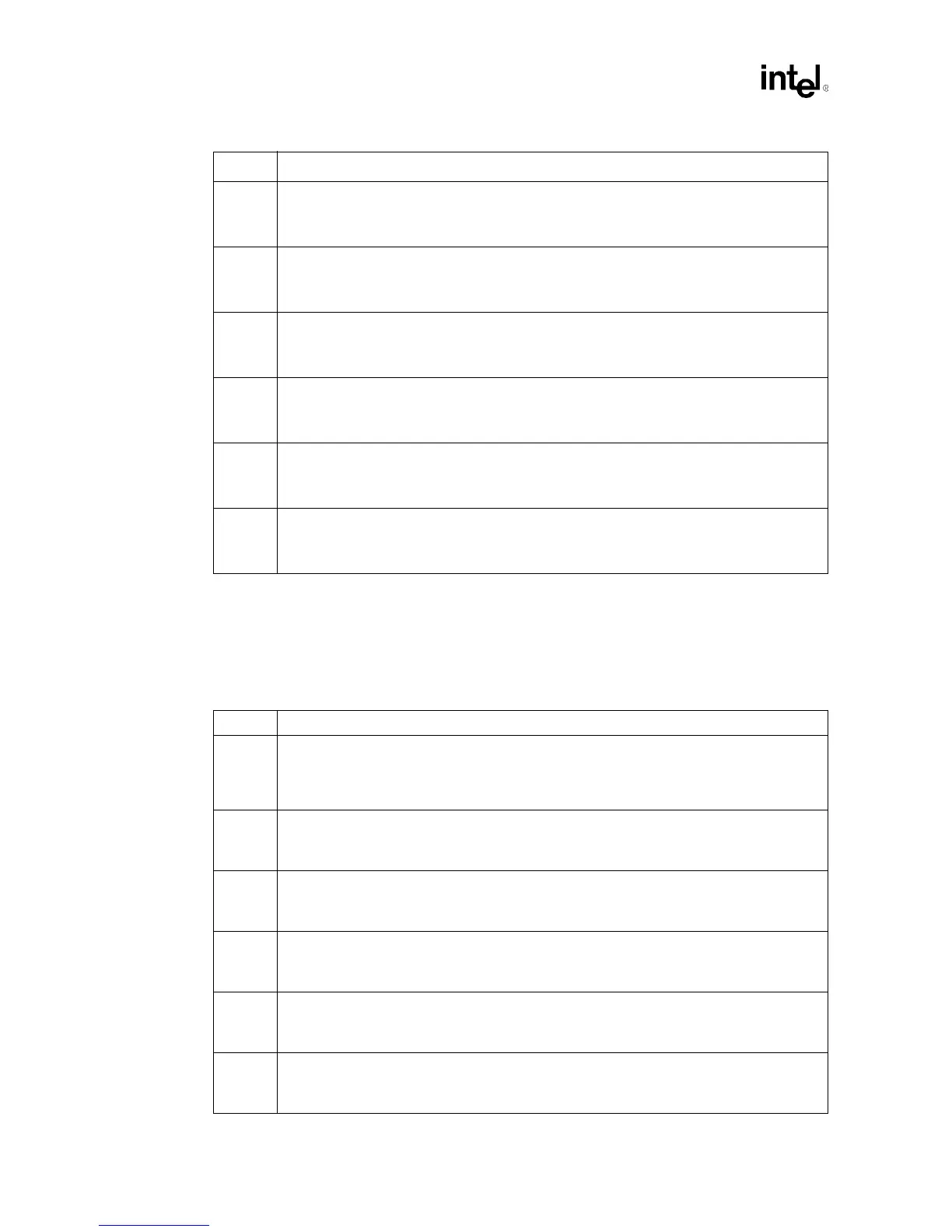

11.1.27.2 Firmware Hub (FWH) Select Register

Address: E8H

Default Value: 00112233H

Attributes: Read/Write

5 FWH_E8_EN: This enables decoding 512KB of the FWH memory range starting at 4 GB – 1.5 MB

(FFE80000H) to 4 GB – 1 MB (FFEFFFFFH). Additionally, this enables decoding of 512K of

register space starting at (4 GB – 4 MB) - 1.5MB (FFA80000h) to (4 GB – 4 MB) - 1MB

(FFAFFFFFh).

4 FWH_E0_EN: This enables decoding 512 KB of the FWH memory range starting at 4 GB – 2 MB

(FFE00000H) to 4 GB - 1.5 MB (FFE7FFFFH). Additionally, this enables decoding of 512K of

register space starting at (4 GB – 4 MB) – 2MB (FFA00000h) to (4 GB – 4 MB) – 1.5MB

(FFA7FFFFh).

3 FWH_D8_EN: This enables decoding 512 KB of the FWH memory range starting at 4 GB - 2.5 MB

(FFD80000H) to 4 GB - 2 MB (FFDFFFFFH). Additionally, this enables decoding of 512K of

register space starting at (4 GB – 4 MB) - 2.5MB (FF980000h) to (4 GB – 4 MB) - 2 MB

(FF9FFFFFh).

2 FWH_D0_EN: This enables decoding 512 KB of the FWH memory range starting at 4 GB - 3 MB

(FFD00000H) to 4 GB - 2.5 MB (FFD7FFFFH). Additionally, this enables decoding of 512K of

register space starting at (4 GB – 4 MB) - 3.0MB (FF900000h) to 4 GB – 4 MB) - 2.5 MB

(FF97FFFFh)

8

.

1 FWH_C8_EN: This enables decoding 512 KB of the FWH memory range starting at 4 GB - 3.5 MB

(FFC80000H) to 4 GB - 3 MB (FFCFFFFFH). Additionally, this enables decoding of 512K of

register space starting at (4 GB – 4 MB) - 3.5MB (FF880000h) to (4 GB – 4 MB) - 3MB

(FF8FFFFFh)

8

.

0 FWH_C0_EN: This enables decoding 512 KB of the FWH memory range starting at 4 GB – 4 MB

(FFC00000H) to 4 GB - 3.5 MB (FFC7FFFFH). Additionally, this enables decoding of 512K of

register space starting at (4 GB – 4 MB) – 4MB (FF800000h) to (4 GB – 4 MB) - 3.5MB

(FF87FFFFh).

Bit Description

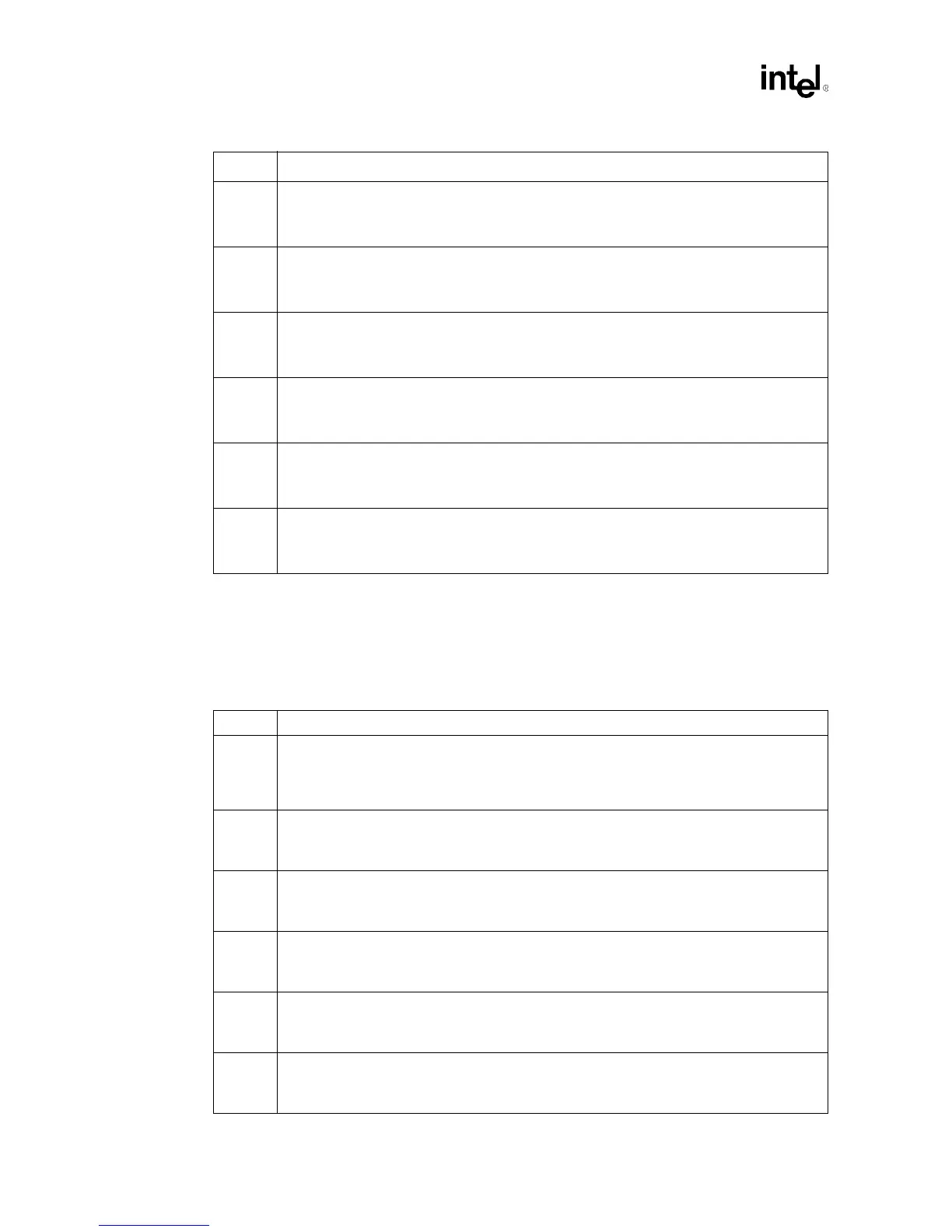

Bit Description

31:28 FWH_F8_IDSEL: This dictates the IDSEL of 512 KB of the FWH memory range starting at 4 GB -

512 KB (FFF80000H) to the top 4 GB (FFFFFFFFH) as well as register space starting at (4 GB-

4MB) - 512KB (FFB80000h) to the top 4 GB - 4MB (FFBFFFFFh). In addition, the upper 128 KB of

this range is shadowed at the top of 1 MB (000E0000H - 000FFFFFH). The enable for this range is

controlled through bit 7 of the FWH Decode Enable Register at E3H.

27:24

FWH_F0_IDSEL: This dictates the IDSEL of 512 KB of the FWH memory range starting at 4 GB -

1 MB (FFF00000H) to 4 GB - 512 KB (FFF7FFFFH) as well as register space starting at (4 GB-

4MB) - 1MB (FFB00000h) to (4 GB-4MB) - 512KB (FFB7FFFFh). The enable for this range is

controlled through bit 6 of the FWH Decode Enable Register at E3H.

23:20

FWH_E8_IDSEL: This dictates the IDSEL of 512 KB of the FWH memory range starting at 4 GB -

1.5 MB (FFE80000H) to 4 GB - 1 MB (FFEFFFFFH) as well as register space starting at (4 GB-

4MB) - 1.5MB (FFA80000h) to (4 GB-4MB) - 1MB (FFAFFFFFh). The enable for this range is

controlled through bit 5 of the FWH Decode Enable Register at E3H.

19:16

FWH_E0_IDSEL: This dictates the IDSEL of 512 KB of the FWH memory range starting at 4 GB -

2 MB (FFE00000H) to 4 GB - 1.5 MB (FFE7FFFFH) as well as register space starting at (4 GB-

4MB) - 2MB (FFA00000h) to (4 GB-4MB) - 1.5MB (FFA7FFFFh). The enable for this range is

controlled through bit 4 of the FWH Decode Enable Register at E3H.

15:12

FWH_D8_IDSEL: This dictates the IDSEL of 512 KB of the FWH memory range starting at 4 GB -

2.5 MB (FFD80000H) to 4 GB - 2 MB (FFDFFFFFH) as well as register space starting at (4 GB-

4MB) - 2.5MB (FF980000h) to (4 GB-4MB) - 2MB (FF9FFFFFh). The enable for this range is

controlled through bit 3 of the FWH Decode Enable Register at E3H.

11:8

FWH_D0_IDSEL: This dictates the IDSEL of 512 KB of the FWH memory range starting at 4 GB -

3 MB (FFD00000H) to 4 GB - 2.5 MB (FFD7FFFFH) as well as register space starting at (4 GB-

4MB) - 3.0MB (FF900000h) to (4 GB-4MB) - 2.5MB (FF97FFFFh). The enable for this range is

controlled through bit 2 of the FWH Decode Enable Register at E3H.

Loading...

Loading...