LPC/FWH Interface Configuration

11-16 Intel® 460GX Chipset Software Developer’s Manual

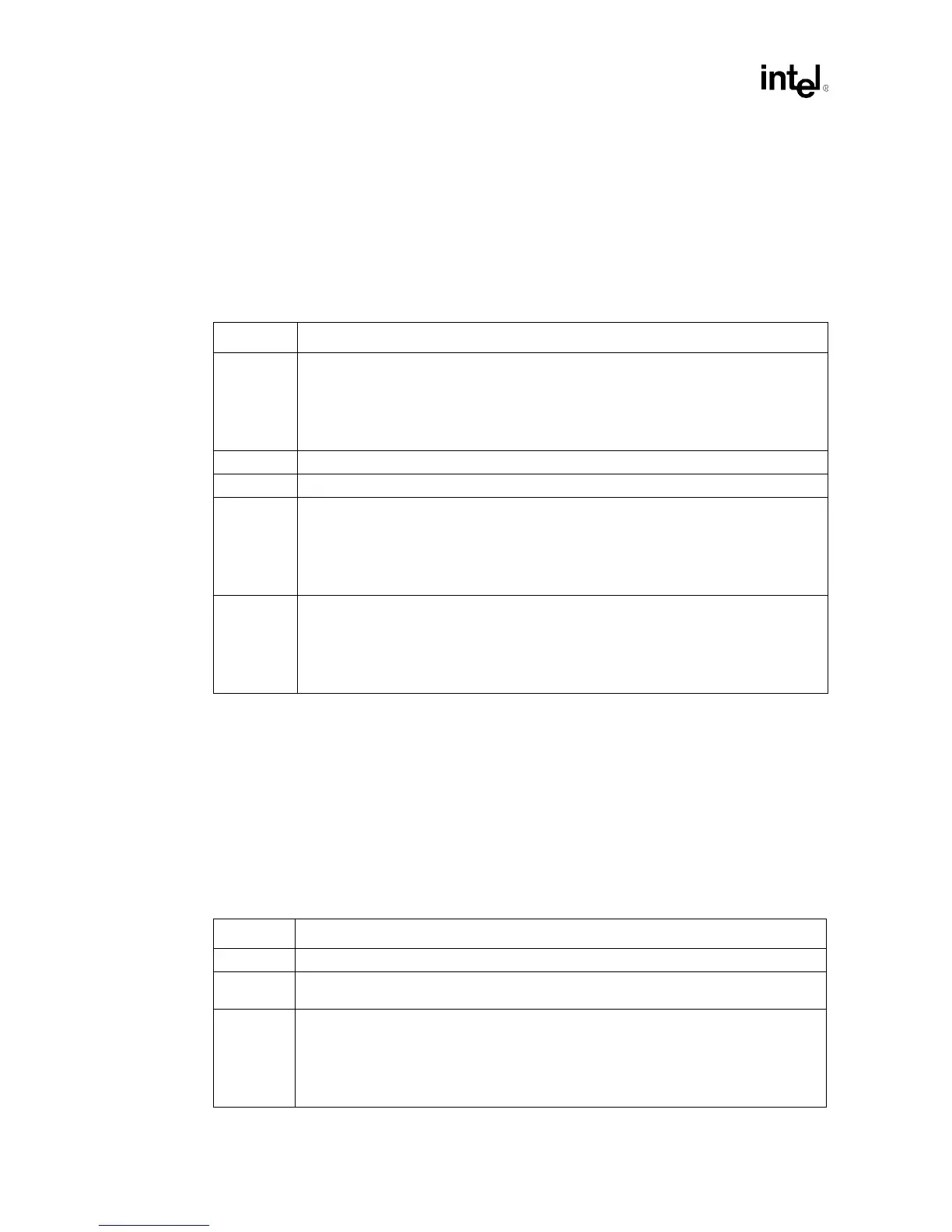

11.2.1.2 Dcm–Dma Channel Mode Register (I/O)

I/O Address: Channels 0-3=0Bh; Channels 4-7=0D6h

Default Value: Bits[7:2]=0; Bits[1:0]=undefined (CPURST or Master Clear)

Attribute: Write Only

Each channel has a 6-bit DMA Channel Mode Register. The Channel Mode Registers provide

control over DMA transfer type, transfer mode, address increment/decrement, and auto-

initialization.

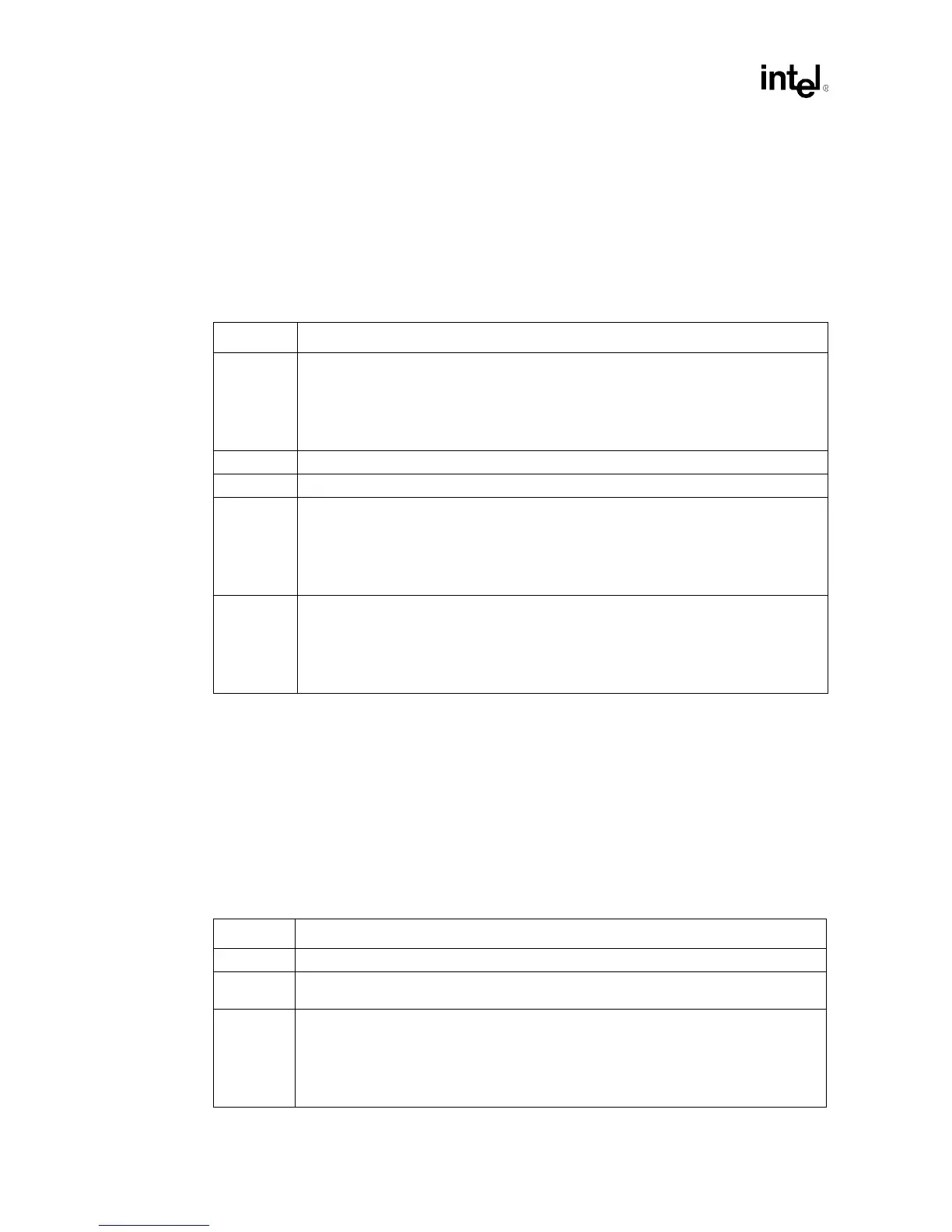

11.2.1.3 Dr–Dma Request Register (I/O)

I/O Address: Channels 0-3–09h; Channels 4-7–0D2h

Default Value: Bits[1:0]=undefined; Bits[7:2]=0 (CPURST or Master Clear)

Attribute: Write Only

The Request Register is used by software to initiate a DMA request. The DMA responds to the

software request as though DREQx is asserted. These requests are non-maskable and subject to

prioritization by the priority encoder network. For a software request, the channel must be in Block

Mode. The Request Register status for DMA1 and DMA2 is output on bits [7:4] of a Status

Register read.

Bit Description

7:6 DMA Transfer Mode. Each DMA channel can be programmed in one of four different modes:

Bits[7:6] Transfer Mode

00 Demand Mode

01 Single Mode

10 Block Mode

11 I Cascade Mode

5 Address Increment/Decrement Select. 0=Increment; 1=Decrement.

4 Auto-initialize Enable. 1=Enable; 0=Disable.

3:2 DMA Transfer Type. When Bits [7:6]=11, the transfer type bits are irrelevant.

Bits[3:2] Transfer Type

00 Verify transfer

01 Write transfer

10 Read transfer

11 I Illegal

1:0 DMA Channel Select. Bits [1:0] select the DMA Channel Mode Register written to by bits [7:2].

Bits[1:0] Channel

00 Channel 0 (4)

01 Channel 1 (5)

10 Channel 2 (6)

11 Channel 3 (7)

Bit Description

7:3 Reserved. Must be 0

2 DMA Channel Service Request. 0=Resets the individual software DMA channel request bit.

1=Sets the request bit. Generation of a TC also sets this bit to 0.

1:0 DMA Channel Select. Bits [1:0] select the DMA channel mode register to program with bit 2.

Bits[1:0] Channel

00 Channel 0

01 Channel 1 (5)

10 Channel 2 (6)

11 Channel 3 (7)

Loading...

Loading...