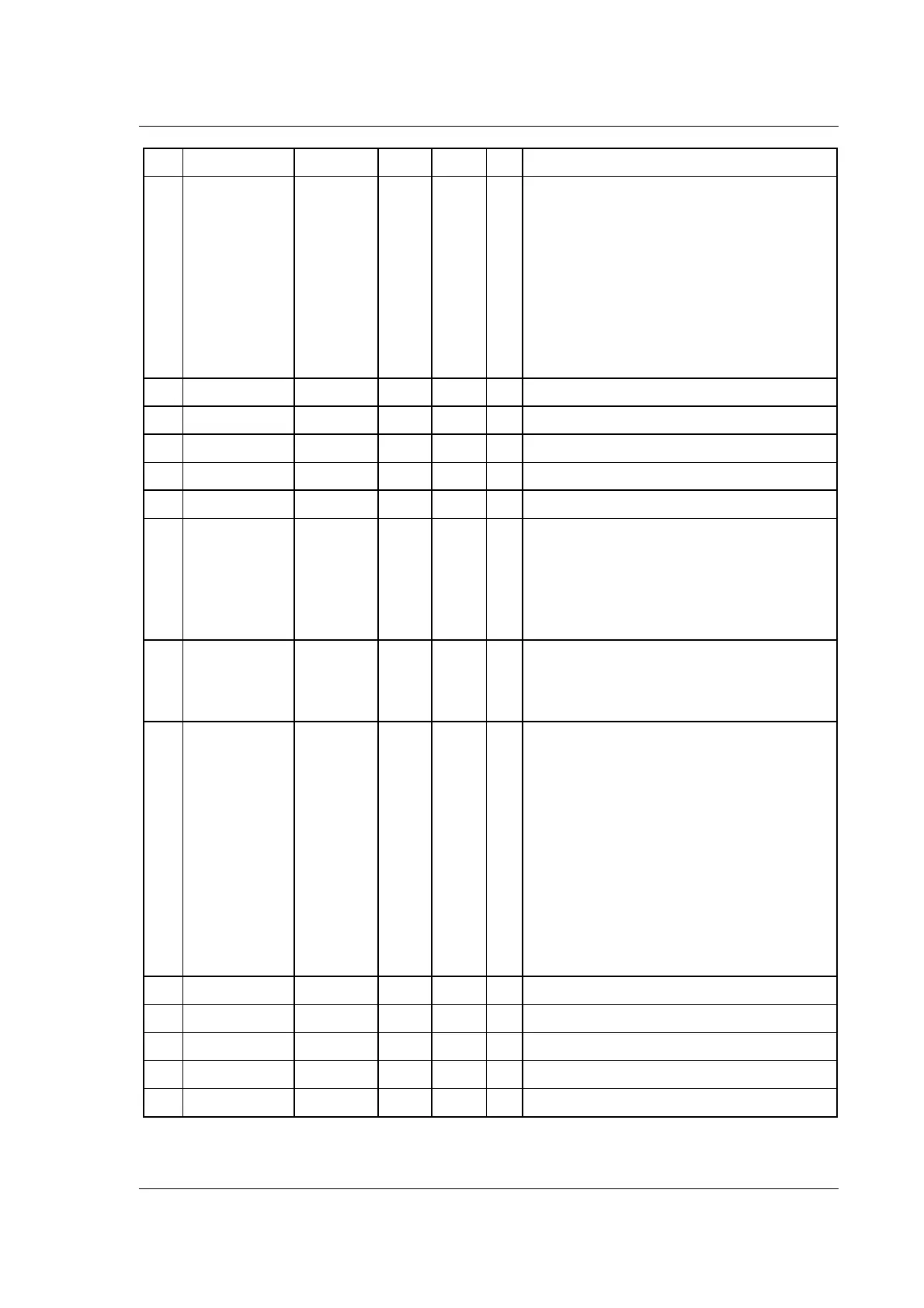

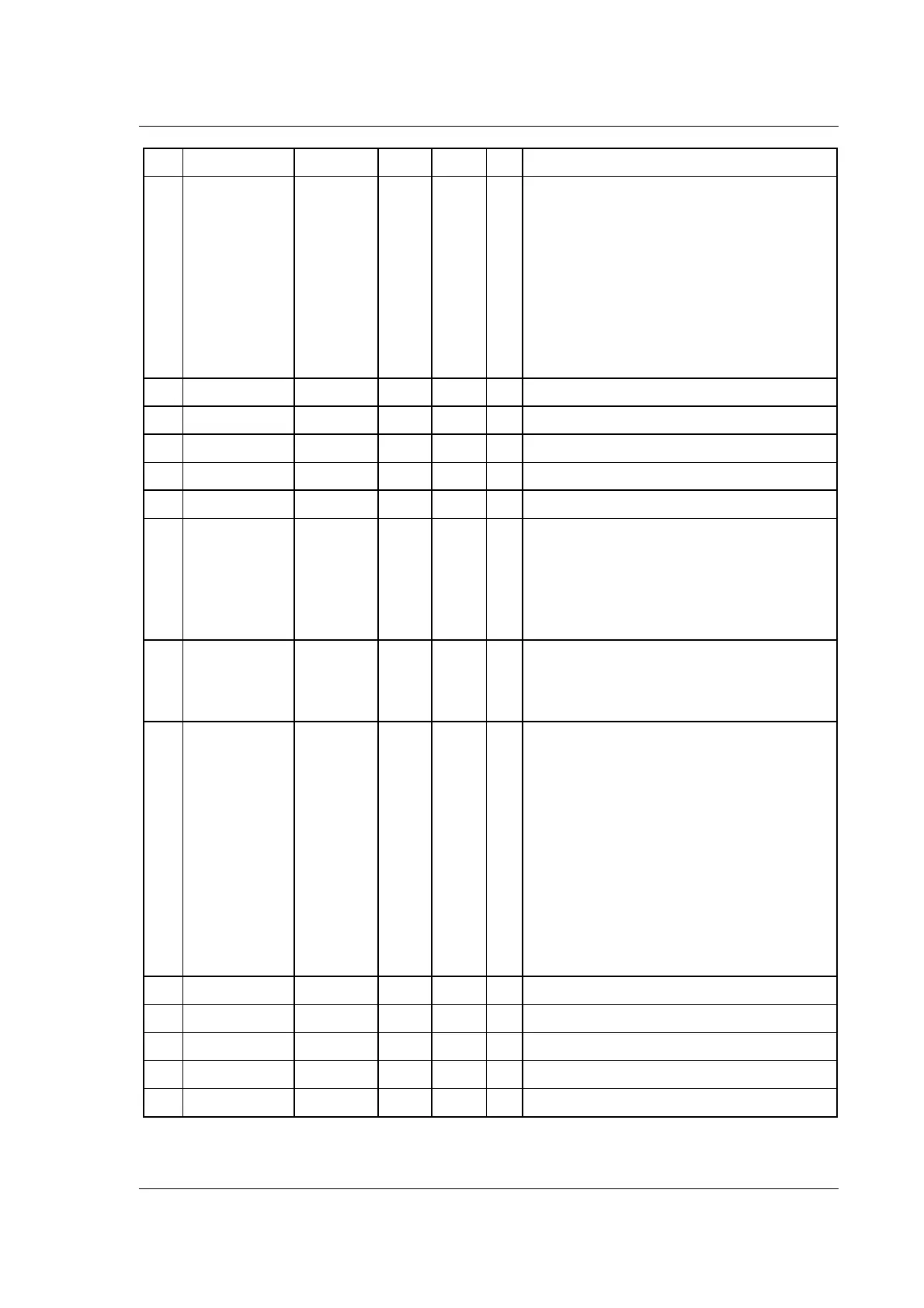

JVL Industri Elektronik A/S - User Manual - Ethernet for MAC and MIS motors 285

12.3 Motor registers MAC400 - 4500

TT1510GB

Reg.

Nr.

Firmware /

MacRegIo Name

MacTalk

Name

Range/

Default

Size /

Access

Unit

Description

107

ent)

Na /

0

Word /

RW

-

Shows various status bits for the currently mounted Gen2

module.

For the MAC00-B41:

Bit 0: Digital Output overload. This shows the staus of the

output driver chip that controls the six digital outputs. The

overload status can be set if either an overcurrent

condition or a too high temperature is detected. This

status bit is cleared when these conditions are no longer

present.

Bit 1: CVO voltage detected. This bit reflects if the voltage

at the CVO terminal is above a hardwired default value.

CVO is the supply voltage for the digital outputs.

108

(not present)

Na /

0

Word /

RW

-

N/U

109

(not present)

Na /

0

Word /

RW

-

N/U

110

(not present)

Na /

0

Word /

RW

-

N/U

111

(not present)

Na /

0

Word /

RW

-

N/U

112

(not present)

Na /

0

Word /

RW

-

N/U

113

B41_DO /

Digital outputs

I/O

management

Na /

0

Word /

RW

-

Bits [5:0] of this register controls the digital outputs O6..O1

on the MAC00-B41 module. Each bit that is set here will

enable the corresponding PNP output.

It is possible to overwrite these bits by using Registers

115-120, see below.

Also Reg215, IO_POLARITY, will invert the value of these

bits before there are written to the hardware.

114

B41_DOSTATUS

I/O

management

Na /

0

Word /

RW

-

Shows the status of each of the six digital outputs actually

written to the hardware.

This value will be Reg113, possibly modified by Regs115 -

120 and finally possibly having some bits inverted by

Reg215.

115

MAC00_10 /

B41_CONF0

(not present)

Na /

0

Word /

RW

-

Controls

IO1

on MAC00-B41 (bit 0 in B41_DO).

Each of the B41_CONF5..CONF0 registers can be used

to modify the corresponding digital outputs by effectively

overwriting bits [5:0] in Reg113, B41_DO.

They can be set to replace the corresponding bit in

B41_DO with any bit from any motor register in the range

1..254, typically status bits from Reg35, ERR_STAT, for

instance bits INPOS or ANY_ERR.

Bits [31:24]: reserved

Bits [23:16]: Source register number, 1..254.

Bits [15:5]: Reserved

Bits [4:0]: Bit number in source register to use.

Reg215, IO_POLARITY, will be applied after these

registers to allow general inversion of each digital output

bit.

116 MAC00_11 /

B41_CONF1

(not present)

Na /

0

Word /

RW

-

Controls

IO2

on MAC00-B41 (bit 1 in B41_DO).

See Reg115, B41_CONF0 for description.

117

B41_CONF2

(not present)

Na /

0

Word /

RW

-

Controls

IO3

on MAC00-B41 (bit 2 in B41_DO).

See Reg115, B41_CONF0 for description.

118

B41_CONF3

(not present)

Na /

0

Word /

RW

-

Controls

IO4

on MAC00-B41 (bit 3 in B41_DO).

See Reg115, B41_CONF0 for description.

119

B41_CONF4

(not present)

Na /

0

Word /

RW

-

Controls

IO5

on MAC00-B41 (bit 4 in B41_DO).

See Reg115, B41_CONF0 for description.

120 MAC

B41_CONF5

(not present)

Na /

0

Word /

RW

-

Controls

IO6

on MAC00-B41 (bit 5 in B41_DO).

See Reg115, B41_CONF0 for description.

Loading...

Loading...