106 CONTENTS

10 HRTC - Hardware Real-Time Controller

10.1 Introduction

The Hardware Real-Time Controller (HRTC) is built into the FPGA. The user can define a sequence of operating

steps to control the way how and when images are exposed and transmitted. Instead using an external PLC, the

time critical acquisition control is directly build into the frame grabber . This is a very unique and powerful feature.

10.1.1 Operating codes

The operating codes for each step can be one of the followings:

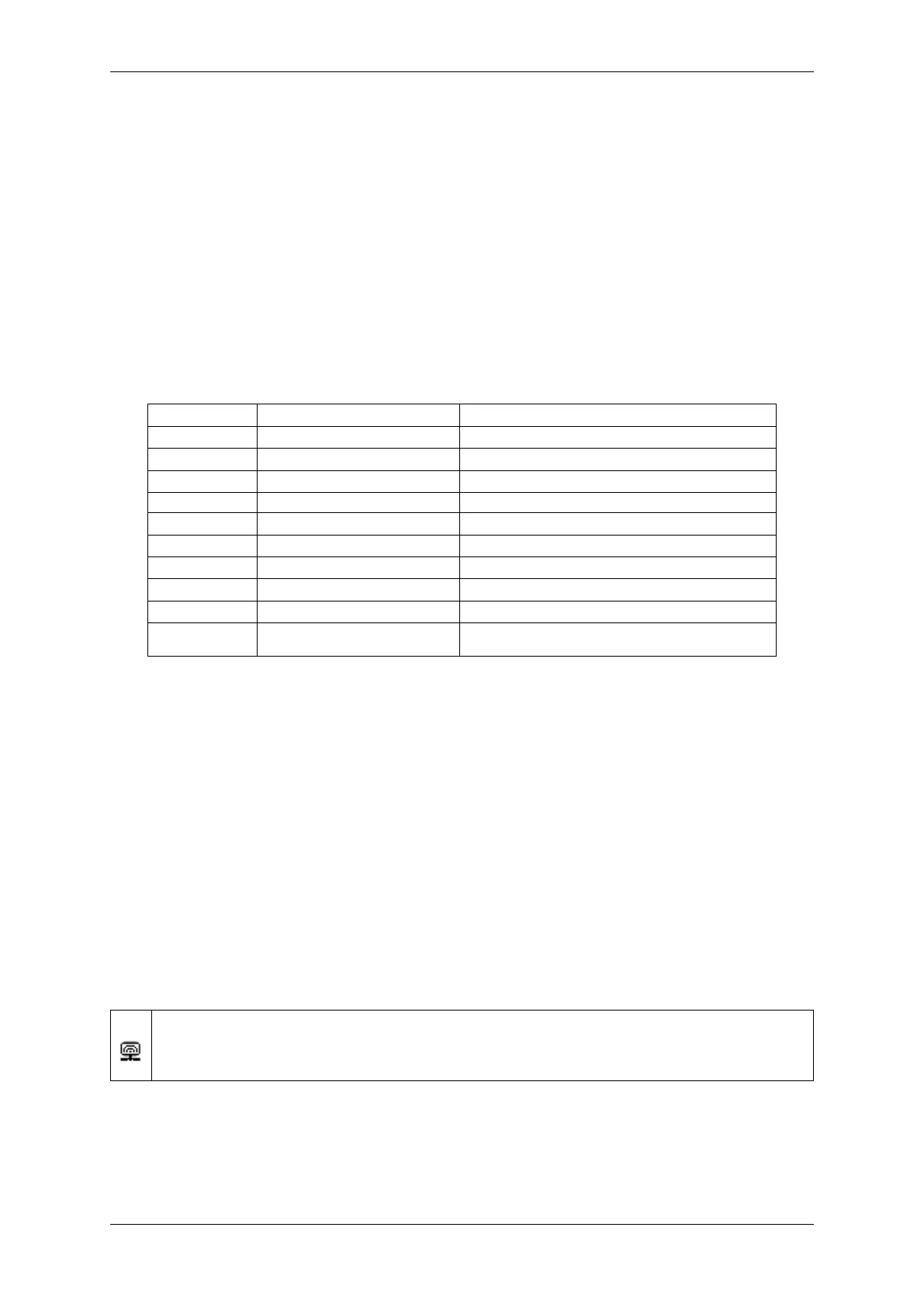

OpCode Parameter Description

Nop - No operation

SetDigout Operation array on dig out Set a digital output

WaitDigin State definition array on dig in Wait for a digital input

WaitClocks Time in us Wait a defined time

Jump HRTC program address Jump to any step of the program

TriggerSet Frame ID Set internal trigger signal to sensor controller

TriggerReset - Reset internal trigger signal to sensor controller

ExposeSet - Set internal expose signal to sensor controller

ExposeReset - Reset internal expose signal to sensor controller

FrameNrReset - Reset internal sensor frame counter

256 HRTC steps are possible.

10.1.2 Program controls

The Hardware Real-Time Controller also supports a basic program control mechanism as the following sample

shows:

0. a = 10

1. a = a - 1

2. WaitClocks 50

3. Jump 0 While a > 0

The section How to use the HRTC (p. 107) should give the impression what everything can be done with the HRTC.

wxPropView - Introduction:

https://www.matrix-vision.com/tl_files/mv11/trainings/wxPropView/wx←-

PropView_HRTC/index.html

MATRIX VISION GmbH

Loading...

Loading...