8.1 mvHYPERION-CLx 37

VIH,

max..min:

3.9V...2.0V (VIH, max = permissible input voltage, which causes an active signal)

VIL,

max..min:

0.8V...-0.3V (VIL, max = permissible input voltage, which causes an inactive signal)

IOL, max: 0.5V (IOL, max = maximum output voltage with internal driven inactive signal)

IL, max: 3.5V (OL, max = maximum input voltage with internal driven inactive signal)

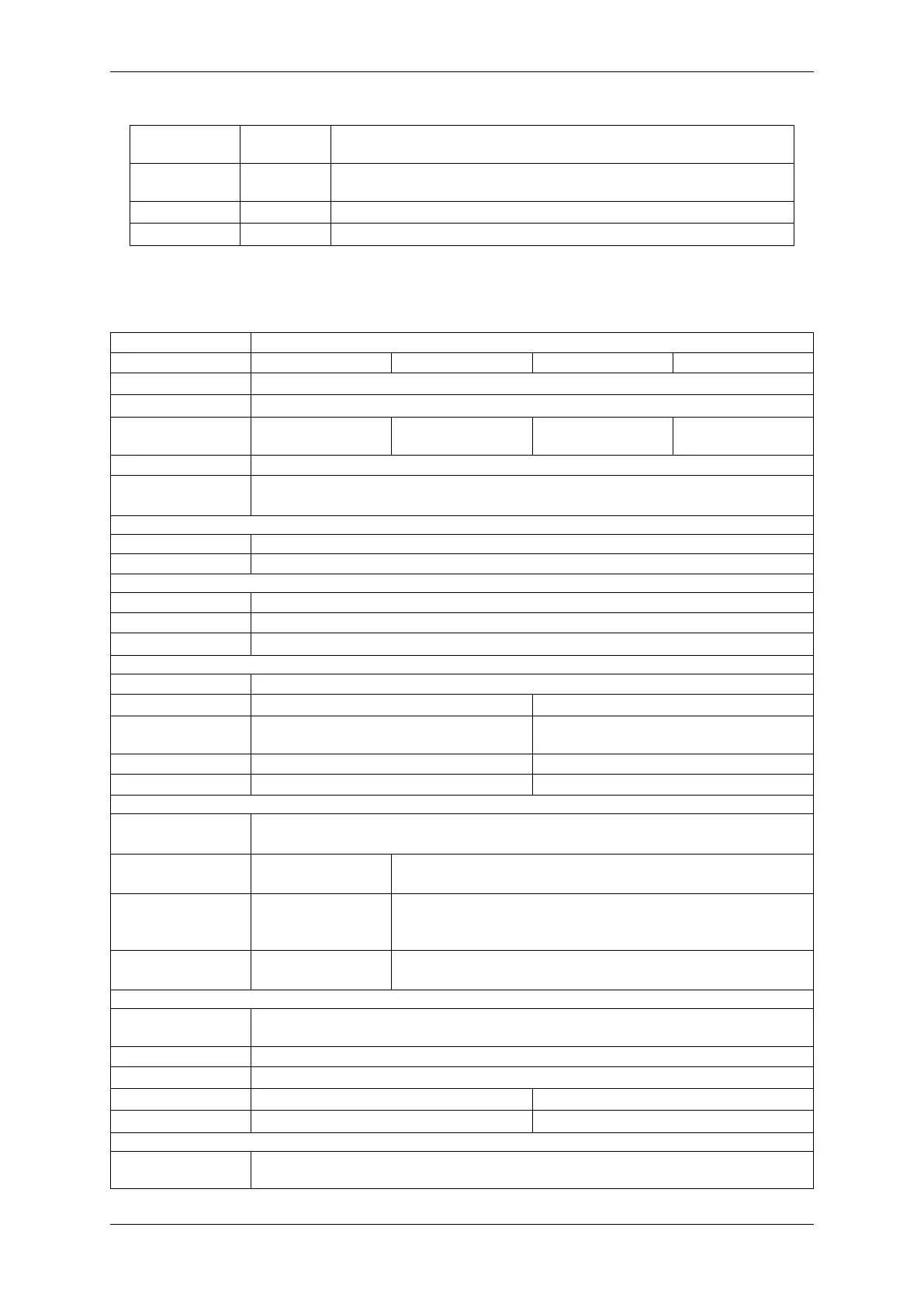

8.1.3 Components

mvHYPERION

-CLb -CLe -CLm -CLf

Video input

Signal format CameraLink ™ (MiniCL)

Video input 1x BASE 2x BASE or 1x M←-

EDIUM

2x BASE or 1x M←-

EDIUM

1x BASE or 1x M←-

EDIUM or 1x FULL

Max. CL clock 85 MHz

Supported CL

specification

1.2

Resolution

Horizontal / vertical 64 K / not limited

Pixel formats

RGB 24 / 30 / 32 bit

Gray 8 / 10 / 12 / 14 / 16 bit

Interface

Bus PCI Express® x1 PCI Express® x4

Continuous data

rate

Max. 200 MB/s Max. 620 MB/s

Peak data rate Max. 250 MB/s Max. 1 GB/s

Payload size Up to 512 Bytes Up to 256 Bytes

Digital in and out-

puts

Trigger-In 1, differential, opto-

isolated, 5 to 24V

2, differential, opto-isolated, 5 to 24V

Strobe-Out 1, differential, opto-

isolated, max. 30V,

100mA

2, differential, opto-isolated, max. 30V, 100mA

Sync-In 1, differential, opto-

isolated, 5 to 24V

2, differential, opto-isolated, 5 to 24V

Current consump-

tion

PCIe 3.3V Max. 1A

PCIe 12V Max. 0.05A + camera power

Camera supply Via PCI Express® 12V max. 0.7A fused Via PCI Express® 12V max. 2A fused

Via additional floppy power plug up to 2A -

Environmental con-

ditions

MATRIX VISION GmbH

Loading...

Loading...