SmartFusion2 SoC FPGA - Cache Controller Configuration - Libero SoC v11.7

Revision 10 11

In this design example, the following application images are created, which can be remapped to the

bottom (0×0000_0000) of the Cortex-M3 processor code region to execute the image:

1. eNVM as a cacheable region.

2. LPDDR as a cacheable region with stack and data segment in the non-cacheable LPDDR

memory.

128 MB of LPDDR memory is selected as a cacheable region and the following 32 KB of LPDDR

is spared for stack and data/heap sections. The stack and data/heap sections of the application

must be allocated in the non-cacheable LPDDR memory region.

3. LPDDR as a cacheable region with stack and data segment in eSRAM.

128 MB of LPDDR memory is selected as a cacheable region, and 32 KB of eSRAM is spared for

stack and data/heap sections.

Firmware Drivers:

The following firmware drivers are used in this application:

• MSS MMUART driver

– To communicate with serial terminal program on the host PC

• MSS Timer driver

– To measure the task execution time

List of APIs:

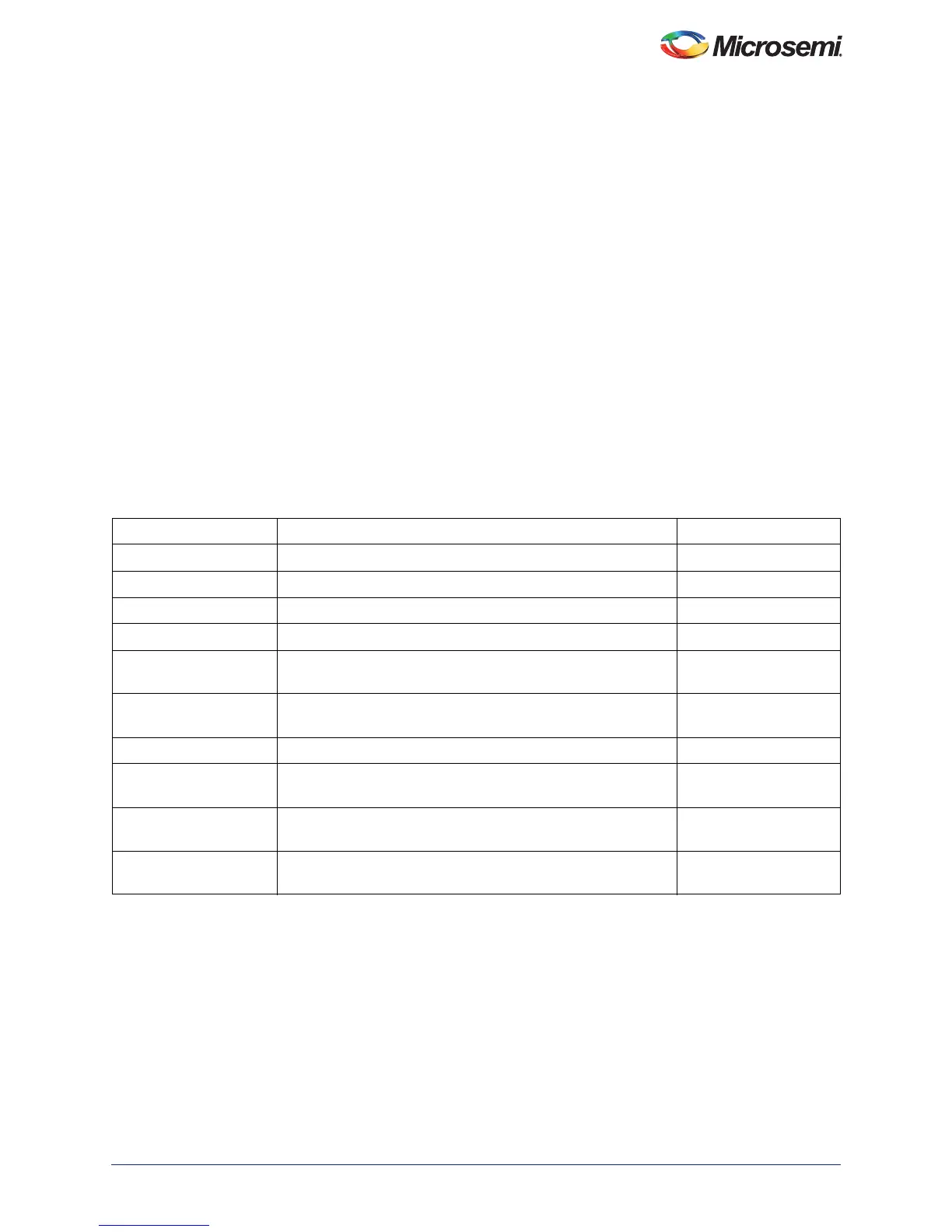

The following APIs in Ta b le 4 are implemented in the software design to configure the cache controller.

Running the Design

This application note provides the following design files and describes the hardware and software

requirements, board settings, and steps to run the design.

• eNVM as cacheable region

• LPDDR as cacheable region with stack and data segment in non cacheable LPDDR memory

• LPDDR as cacheable region with stack and data segment in eSRAM

Table 4 • APIs to Configure the Cache Controller

API Description Input Parameters

MSS_CC_enable Enables the cache memory Void

MSS_CC_disable Disables the cache memory Void

MSS_CC_enable_lock Enables Cache locked mode Void

MSS_CC_disable_lock Disables Cache locked mode Void

MSS_CC_flush_index Flushes one index in the cache memory, which is used to

invalidate all tags of four sets at one index only

Index value

MSS_CC_flush Flushes the cache memory, which is used to invalidate all tags

of four sets at the same time

Void

MSS_CC_set_region Sets the cacheable region size to 128 MB, 256 MB, or 512 MB Cacheable region value

MSS_CC_get_miss_cnt Returns the total number of cache misses that occur in the

cacheable region through ICode bus

Void

MSS_CC_get_hits_cnt Returns the total number of cache hits occur in the cacheable

region through ICode bus

Void

MSS_CC_get_trans_cnt Returns the total number of transaction counts processed by

cache engine

Void

Loading...

Loading...