SmartFusion2 SoC FPGA - Cache Controller Configuration - Libero SoC v11.7

8 Revision 10

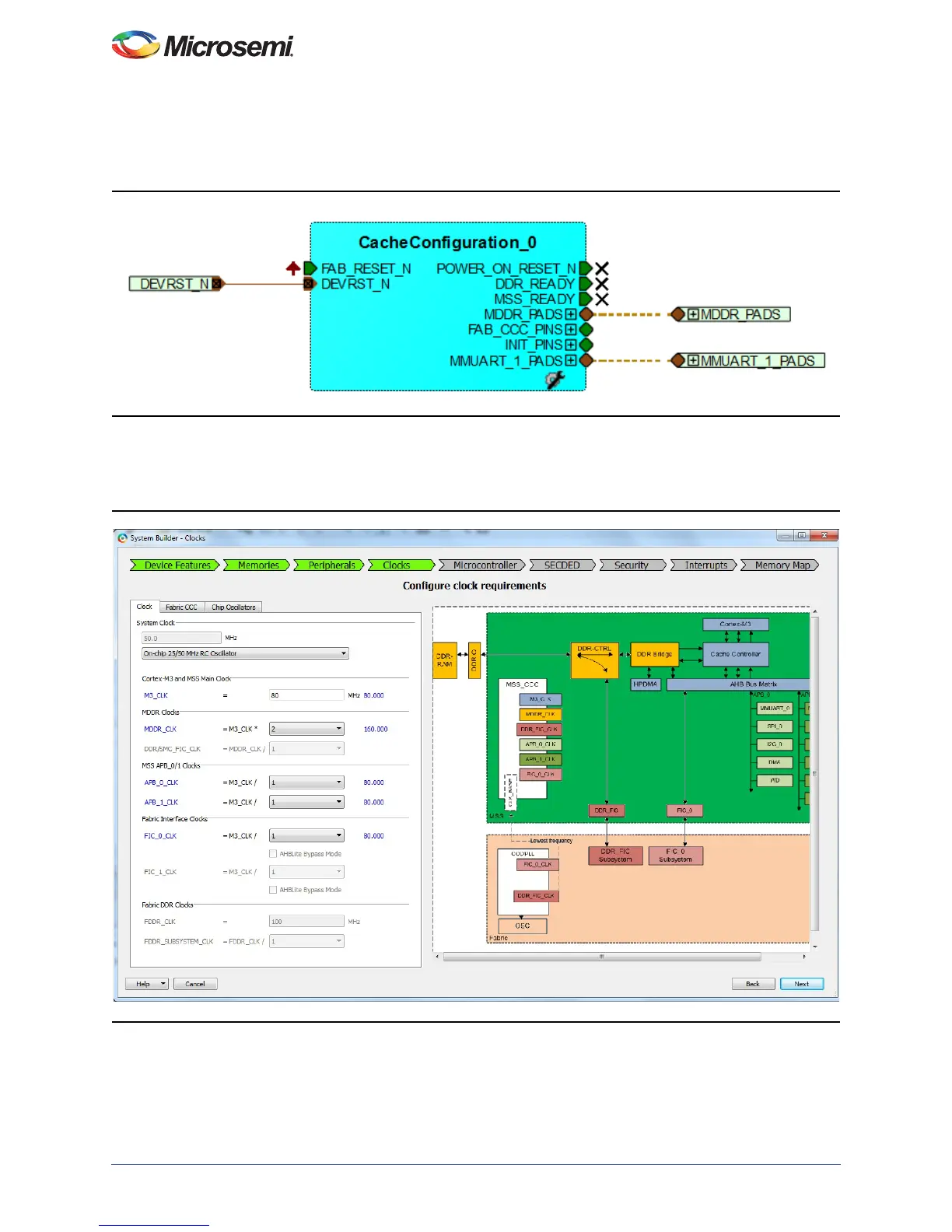

Hardware Implementation

The hardware implementation involves configuring MDDR, MMUART_1, and clocks using System

Builder. Figure 4 shows the top-level SmartDesign of the cache controller configuration.

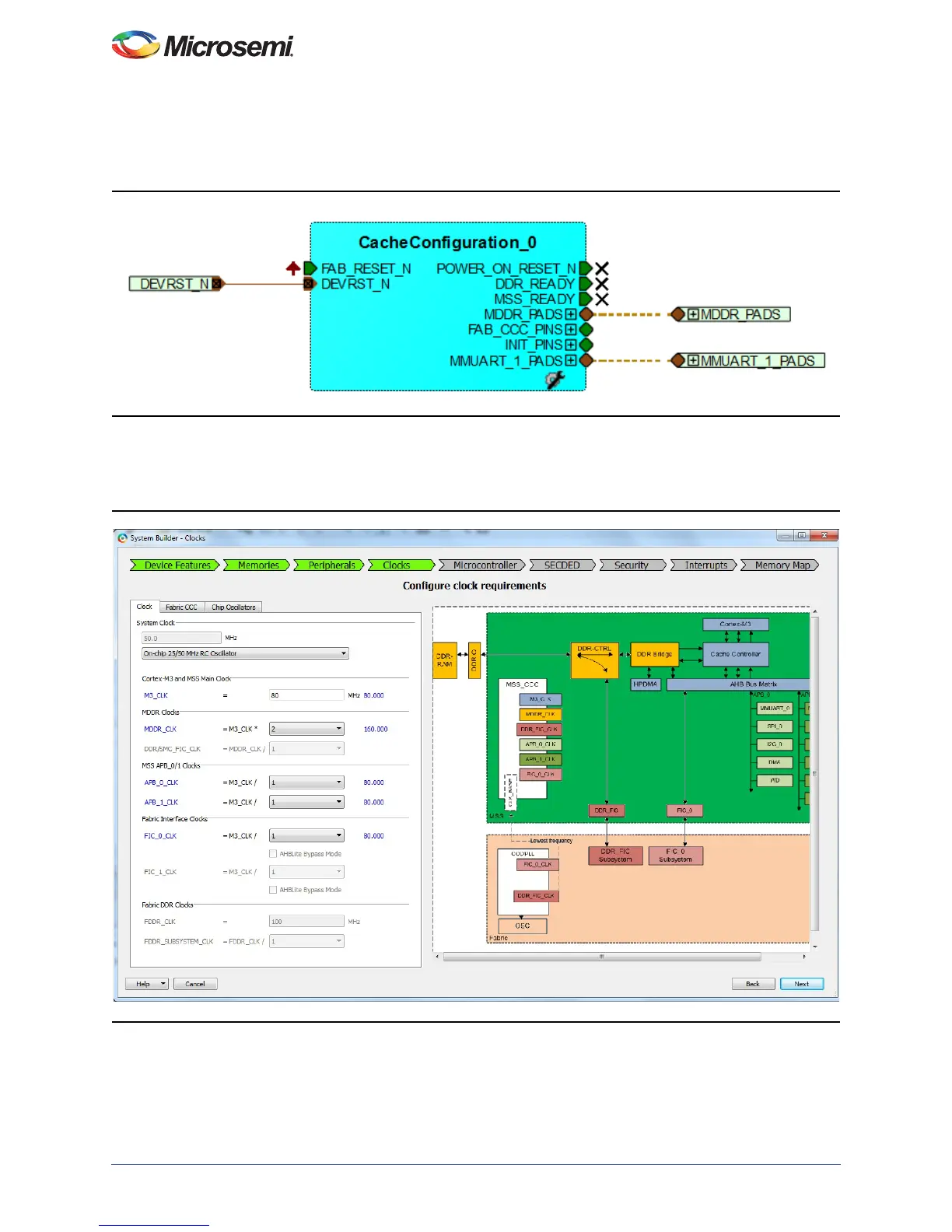

The MSS_CCC clock is sourced from Fabric CCC. Fabric CCC is configured to provide the

80 MHz clock using GL0. Figure 5 shows the system clocks configurations for M3_CLK, MDDR_CLK,

and APB_0_CLK/APB_1_CLK.

Figure 4 • Top-Level SmartDesign

Figure 5 • Clock Configurations

Loading...

Loading...