SmartFusion2 SoC FPGA - Cache Controller Configuration - Libero SoC v11.7

Revision 10 7

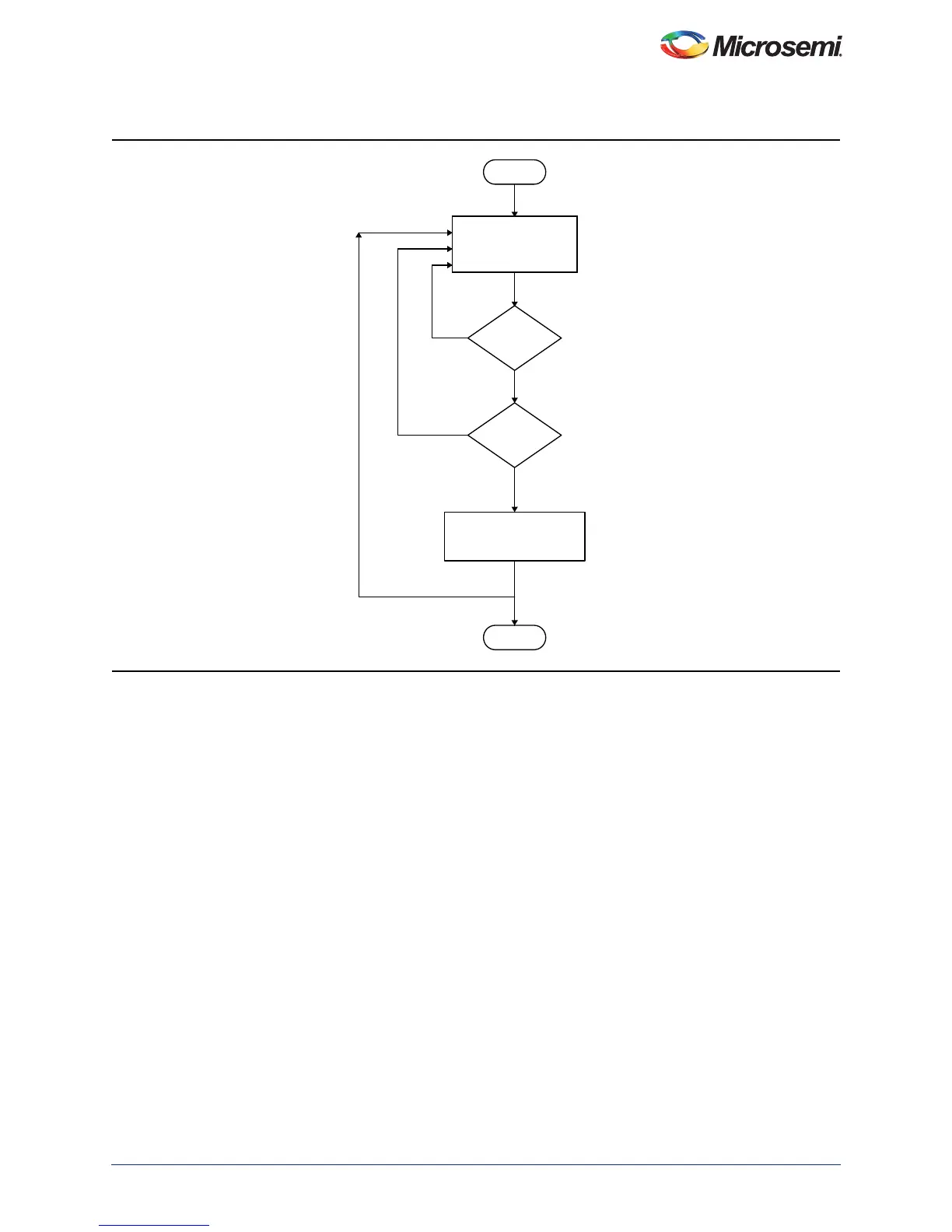

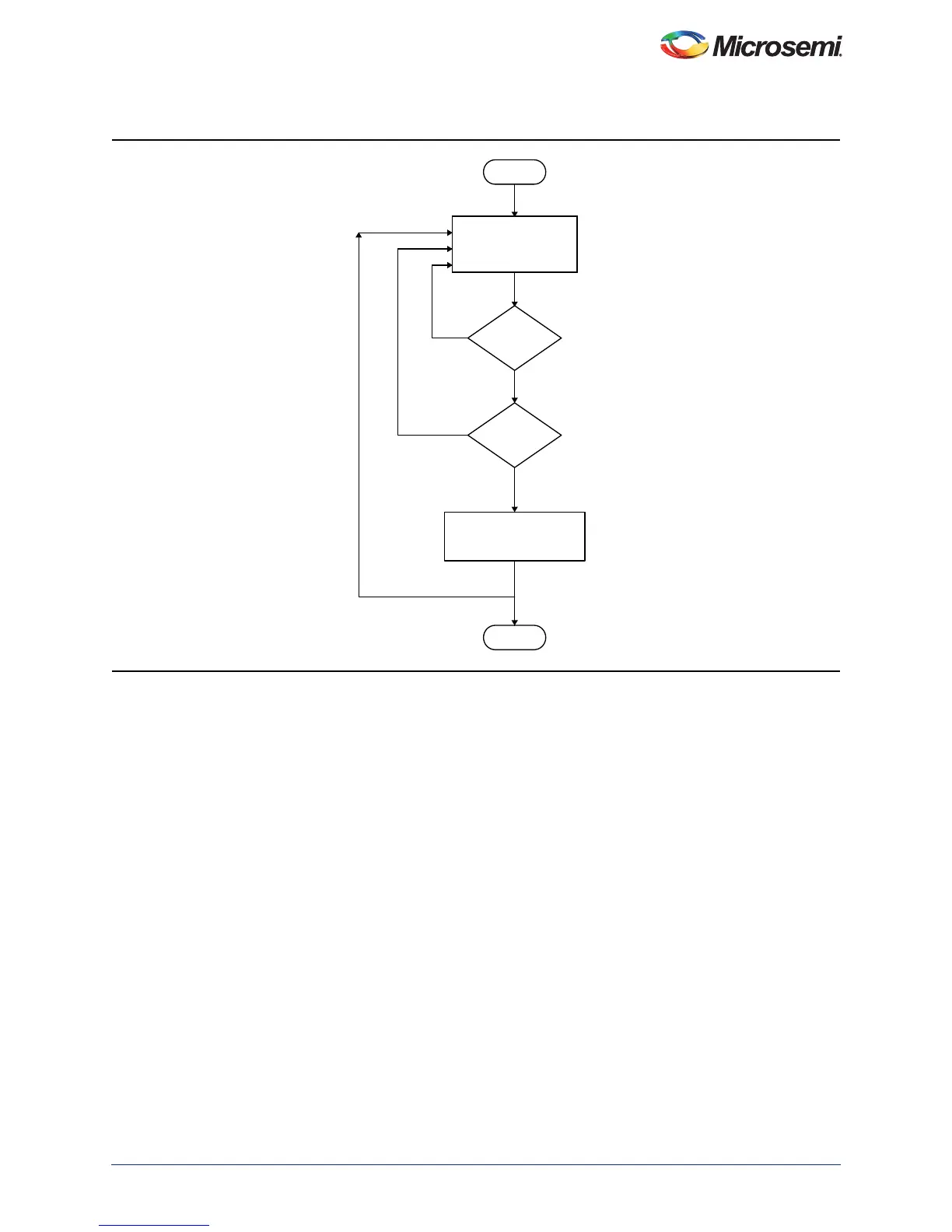

Figure 3 shows a simple program execution flow with Cache Locked mode.

Refer to Table 4 on page 11 for APIs to enable or disable the Cache Locked mode.

Design Description

The example designs use MMUART_1, eSRAM, DDR, and eNVM memory controllers. In the design

example, microcontroller subsystem clock conditioning circuitry (MSS CCC) is configured to run M3_CLK

at 80 MHz, which drives the clock to Cortex-M3 processor. The cache controller can be configured either

using cache controller block in System Builder configurator or through APIs (Table 4 on page 11). The

software application calculates the n

th

Fibonacci number with and without cache controller and compares

the execution time. It also gets the cache status information such as, cache hit, cache miss, cache hit

rate, and cache miss rate. This application also supports cache memory flushing.

Figure 3 • Simple Program Execution Flow with Cache Locked Mode

6WDUW

&RUWH[0

UXQQLQJLQVWUXFWLRQV

:LWKFDFKHPHPRU\

HQDEOHG

,V&DFKH

ORFNHGPRGH

HQDEOHG"

,VQHZ

LQVWUXFWLRQD

FDFKHKLW"

,QVWUXFWLRQLVQRQFDFKHDEOH

UXQQLQJGLUHFWO\IRUPPDLQ

PHPRU\

6WRS

1R

<HV

1R

<HV

3RZHU2II

1H[W,QVWUXFWLRQ

Loading...

Loading...