SmartFusion2 SoC FPGA - Cache Controller Configuration - Libero SoC v11.7

10 Revision 10

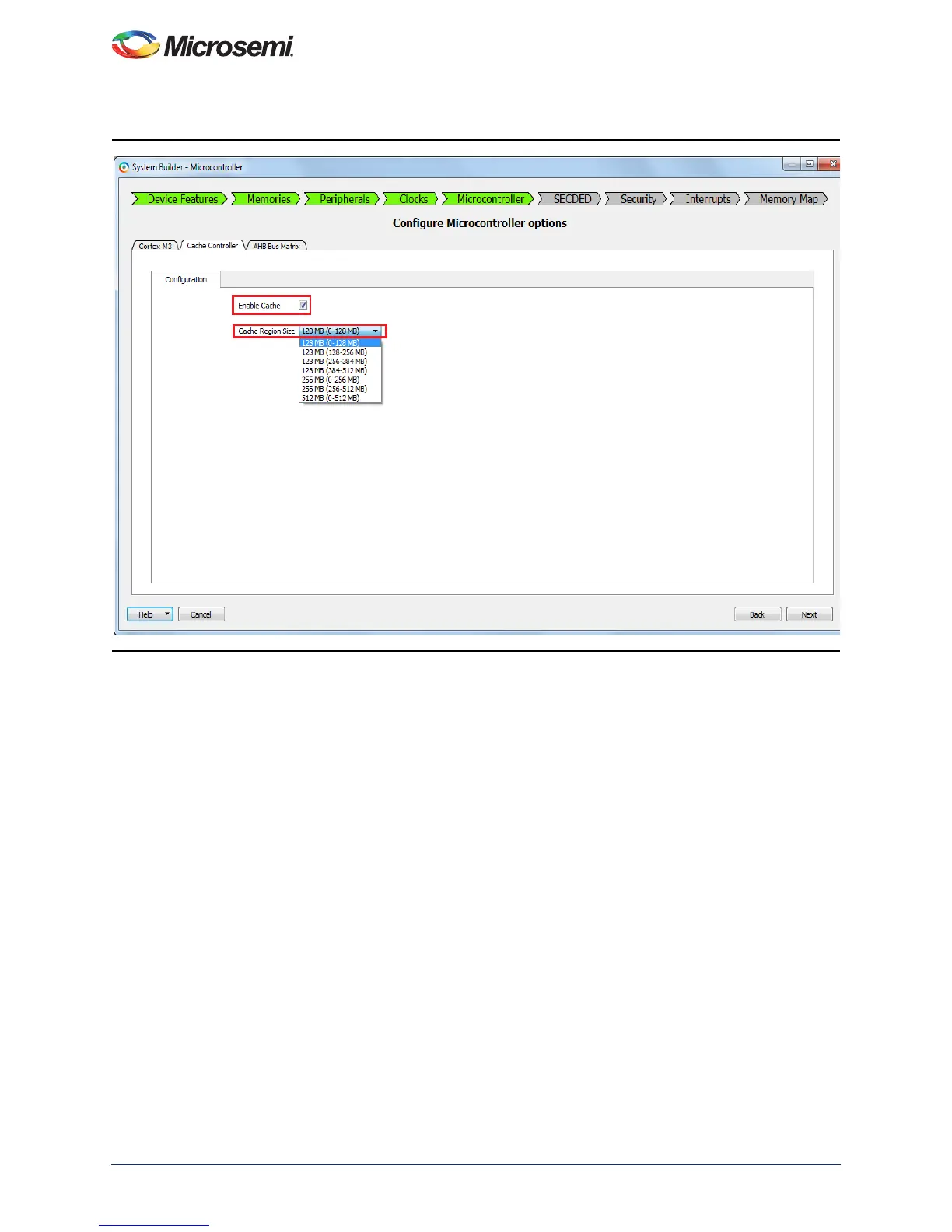

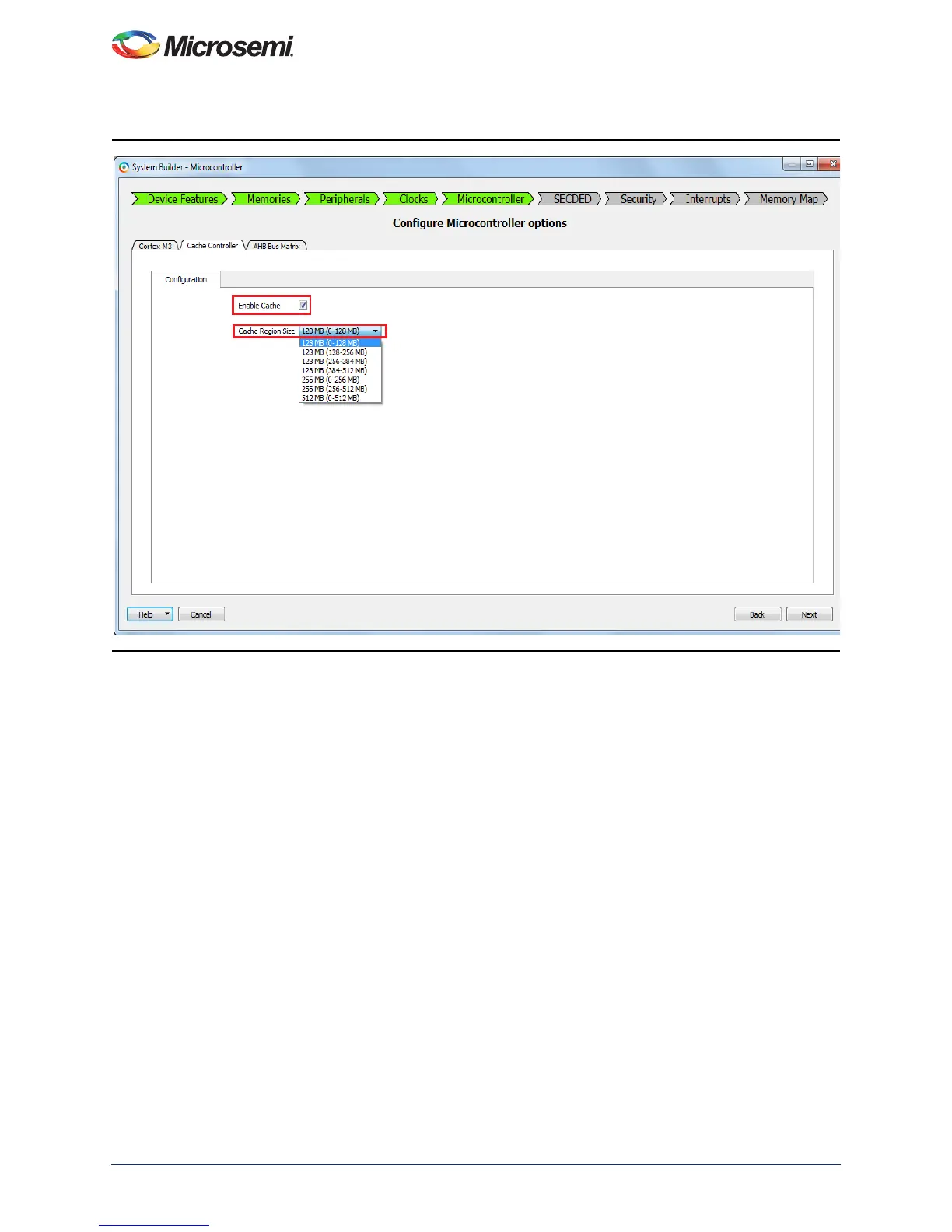

Figure 7 shows the cache controller configuration through System Builder in the Libero SoC software.

Note: Enabling cache through System Builder is not required in this application note design.

Software Implementation

The software design example performs the following operations:

• Enabling or disabling the cache controller

• Selecting cacheable region in case of DDR memory

• Cache memory flushing

• Initialization of timer to measure execution time

• Calculating cache hit rate, cache miss rate, and task execution time

• Displaying results on serial terminal program (for example, HyperTerminal) using MMUART_1

The example software design uses UART based serial communication to communicate with serial

terminal program on the host PC. This example takes finding the n

th

Fibonacci number as the task and

calculates the result with and without cache controller. The Fibonacci number is randomly selected. It

displays the cache hit rate, cache miss rate, and execution time on serial terminal program.

Figure 7 • Cache Controller Configuration Through System Builder in Libero

Loading...

Loading...