SmartFusion2 SoC FPGA - Cache Controller Configuration - Libero SoC v11.7

Revision 10 15

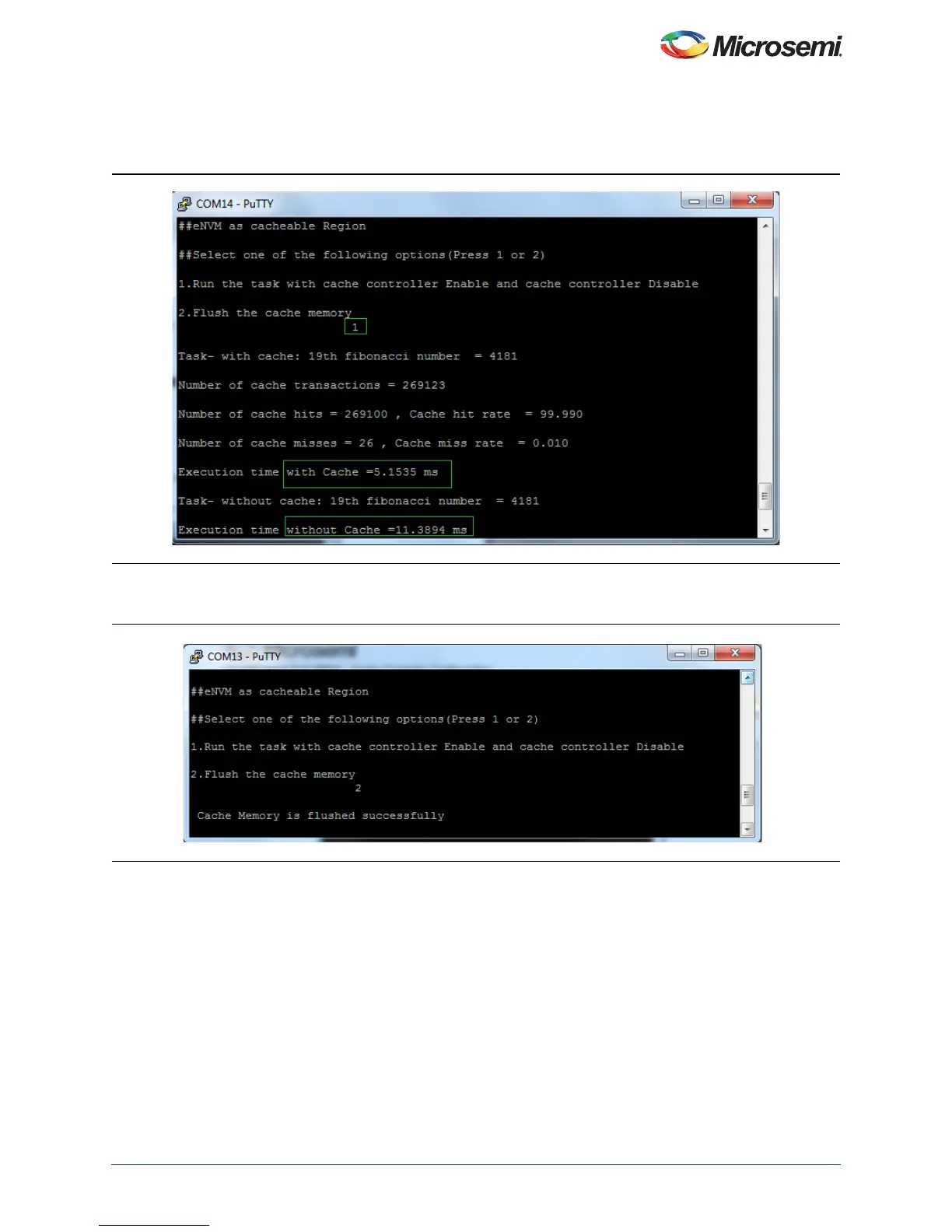

Selecting option 1 executes the task with the cache controller enabled. The application program

calculates the task execution time with cache memory and without cache memory and also

displays the cache status information, as shown in Figure 13.

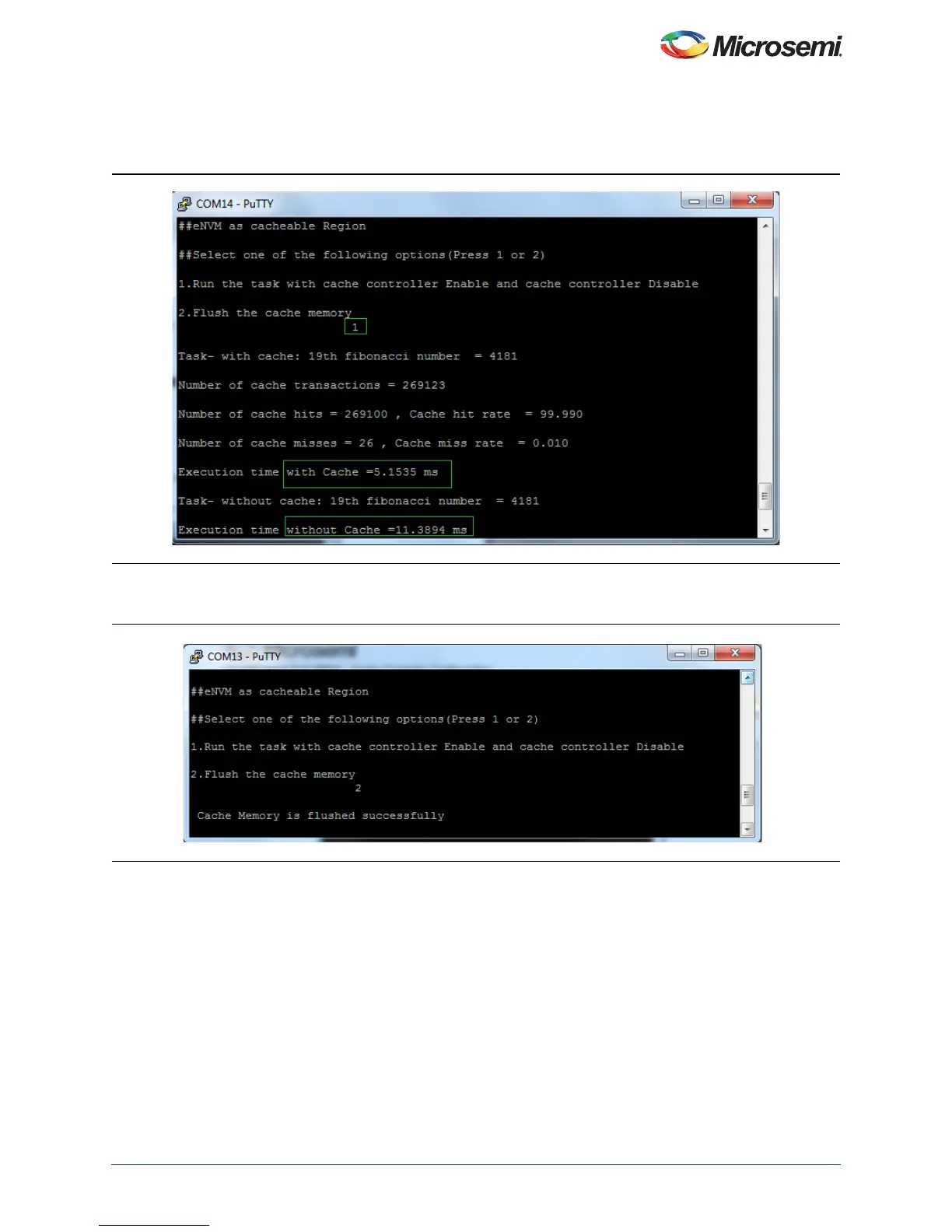

Selecting option 2 flushes the cache memory completely.

Conclusion

This application note explains the cache controller configuration in eNVM and DDR memory remap

modes supported by the SmartFusion2 devices.

Figure 13 • Cache Status Information With Cache Memory Enabled

Figure 14 • Cache Memory Flush

Loading...

Loading...