122

8575

8575

N/B Maintenance

N/B Maintenance

5.5 PCI1410GGU PCMCIA Controller

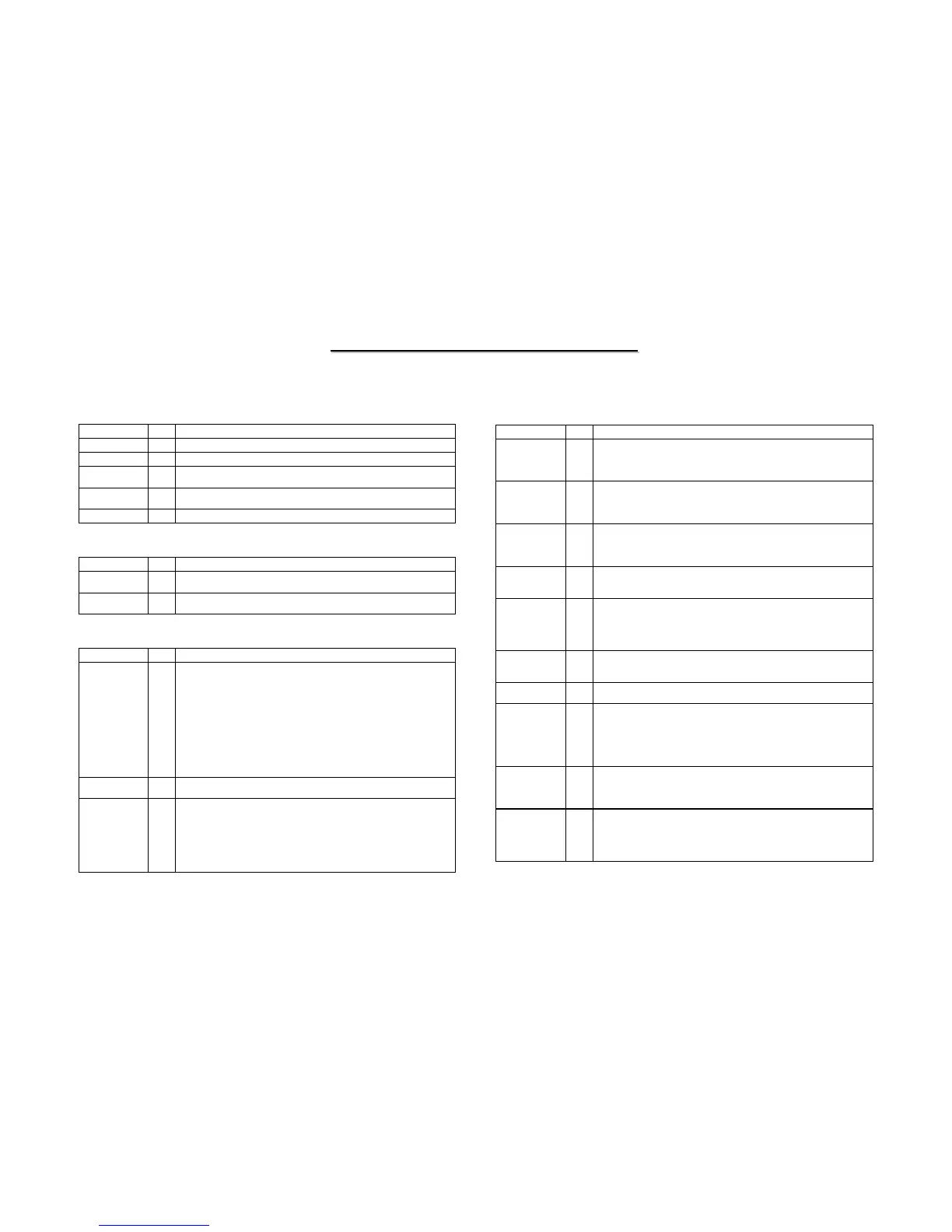

Power Supply

Name I/O Description

GND

Device ground terminals

VCC

Power supply terminal for core logic (3.3V)

VCCCB

Clamp voltage for PC Card interface. Matches card signaling environment,

5 V or 3.3 V.

VCCI

Clamp voltage for interrupt subsystem interface and miscellaneous I/O, 5 V

or 3.3 V

VCCP

Clamp voltage for PCI signaling, 5 V or 3.3 V

PC Card Power Switch

Name I/O Description

VCCD0

VCCD1

O Logic controls to the TPS2211 PC Card power interface switch to control

AVCC.

VPPD0

VPPD1

O Logic controls to the TPS2211 PC Card power interface switch to control

AVPP.

PCI System

Name I/O Description

GRST#

I Global reset. When the global reset is asserted, the GRST# signal causes the

PCI1410 to place all output buffers in a high-impedance state and reset all

internal registers. When GRST# is asserted, the device is completely in its

default state. For systems that require wake-up from D3, GRST# will

normally be asserted only during initial boot. PRST# should be used

following initial boot so that PME context is retained when transitioning

from D3 to D0. For systems that do not require wake-up from D3, GRST#

should be tied to PRST#.

When the SUSPEND# mode is enabled, the device is protected from the

GRST#, and the internal registers are preserved. All outputs are placed in a

high-impedance state, but the contents of the registers are preserved.

PCLK

I PCI bus clock. PCLK provides timing for all transactions on the PCI bus.

All PCI signals are sampled at the rising edge of PCLK.

PRST#

I PCI reset. When the PCI bus reset is asserted, PRST# causes the PCI1410 to

place all output buffers in a high-impedance state and reset internal

registers. When PRST# is asserted, the device is completely nonfunctional.

After PRST is deasserted, the PCI1410 is in a default state.

When the SUSPEND# mode is enabled, the device is protected from the

PRST#, and the internal registers are preserved. All outputs are placed in a

high-impedance state, but the contents of the registers are preserved.

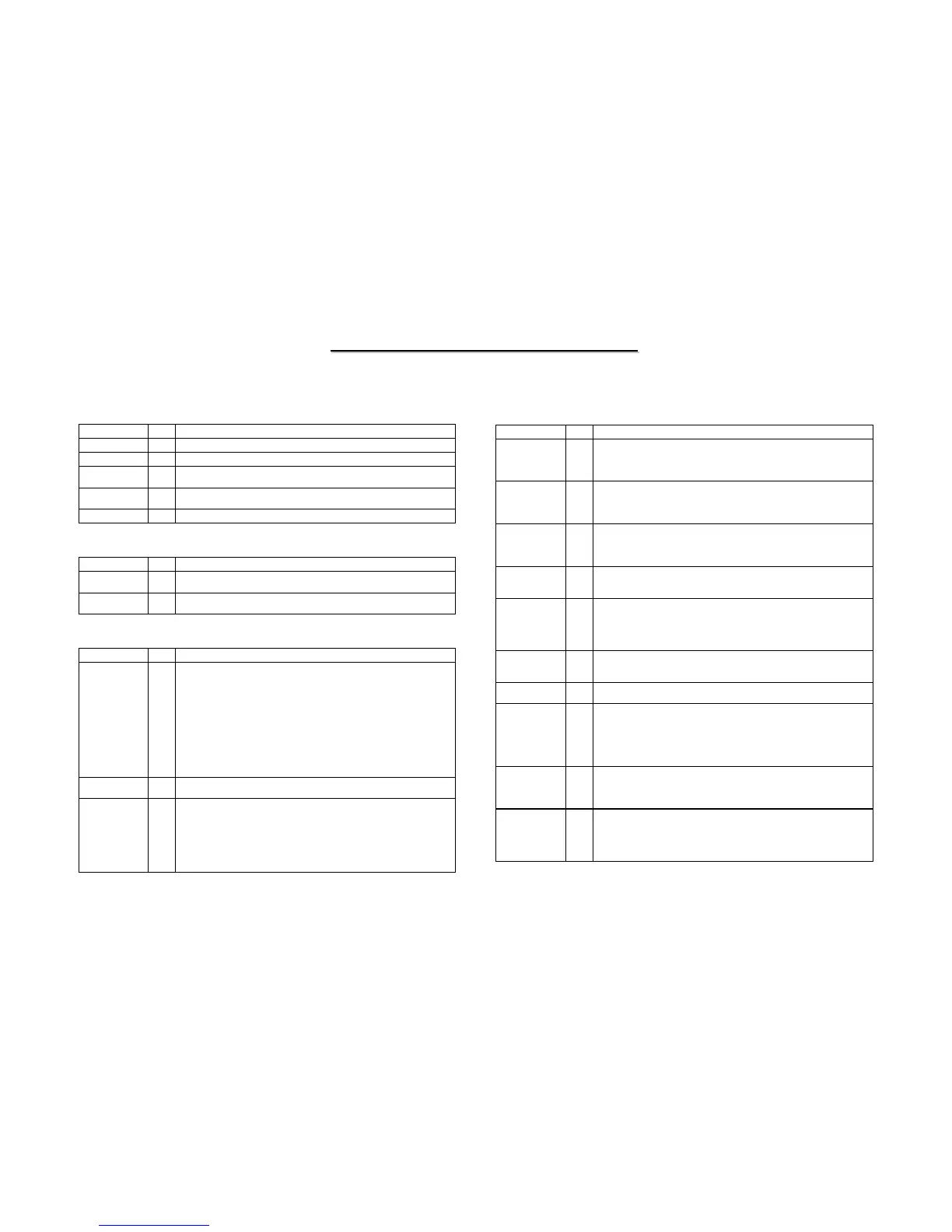

PCI Interface Control

Name I/O Description

DEVSEL#

I/O PCI device select. The PCI1410 asserts DEVSEL# to claim a PCI cycle as

the target device. As a PCI initiator on the bus, the PCI1410 monitors

DEVSEL# until a target responds. If no target responds before timeout

occurs, then the PCI1410 terminates the cycle with an initiator abort.

FRAME#

I/O PCI cycle frame. FRAME# is driven by the initiator of a bus cycle.

FRAME# is asserted to indicate that a bus transaction is beginning, and data

transfers continue while this signal is asserted. When FRAME# is

deasserted, the PCI bus transaction is in the final data phase.

GNT#

I PCI bus grant. GNT# is driven by the PCI bus arbiter to grant the PCI1410

access to the PCI bus after the current data transaction has completed.

GNT# may or may not follow a PCI bus request, depending on the PCI bus

parking algorithm.

IDSEL

I Initialization device select. IDSEL selects the PCI1410 during configuration

space accesses. IDSEL can be connected to one of the upper 24 PCI address

lines on the PCI bus.

IRDY#

I/O PCI initiator ready. IRDY# indicates the PCI bus initiator’s ability to

complete the current data phase of the transaction. A data phase is

completed on a rising edge of PCLK where both IRDY# and TRDY# are

asserted. Until IRDY# and TRDY# are both sampled asserted, wait states

are inserted.

PERR#

I/O PCI parity error indicator. PERR# is driven by a PCI device to indicate that

calculated parity does not match PAR when PERR# is enabled through bit 6

of the command register.

REQ#

O PCI bus request. REQ# is asserted by the PCI1410 to request access to the

PCI bus as an initiator.

SERR#

O PCI system error. SERR# is an output that is pulsed from the PCI1410 when

enabled through bit 8 of the command register indicating a system error has

occurred. The PCI1410 need not be the target of the PCI cycle to assert this

signal. When SERR# is enabled in the command register,

this signal also pulses, indicating that an address parity error has occurred

on a CardBus interface.

STOP#

I/O PCI cycle stop signal. STOP# is driven by a PCI target to request the

initiator to stop the current PCI bus transaction. STOP# is used for target

disconnects and is commonly asserted by target devices that do not support

burst data transfers.

TRDY#

I/O PCI target ready. TRDY# indicates the primary bus target’s ability to

complete the current data phase of the transaction. A data phase is

completed on a rising edge of PCLK when both IRDY# and TRDY# are

asserted. Until both IRDY# and TRDY# are asserted, wait states are

inserted.

Loading...

Loading...