126

8575

8575

N/B Maintenance

N/B Maintenance

5.5 PCI1410GGU PCMCIA Controller

CardBua PC Card Interface Control (Slots A and B) (Continued)

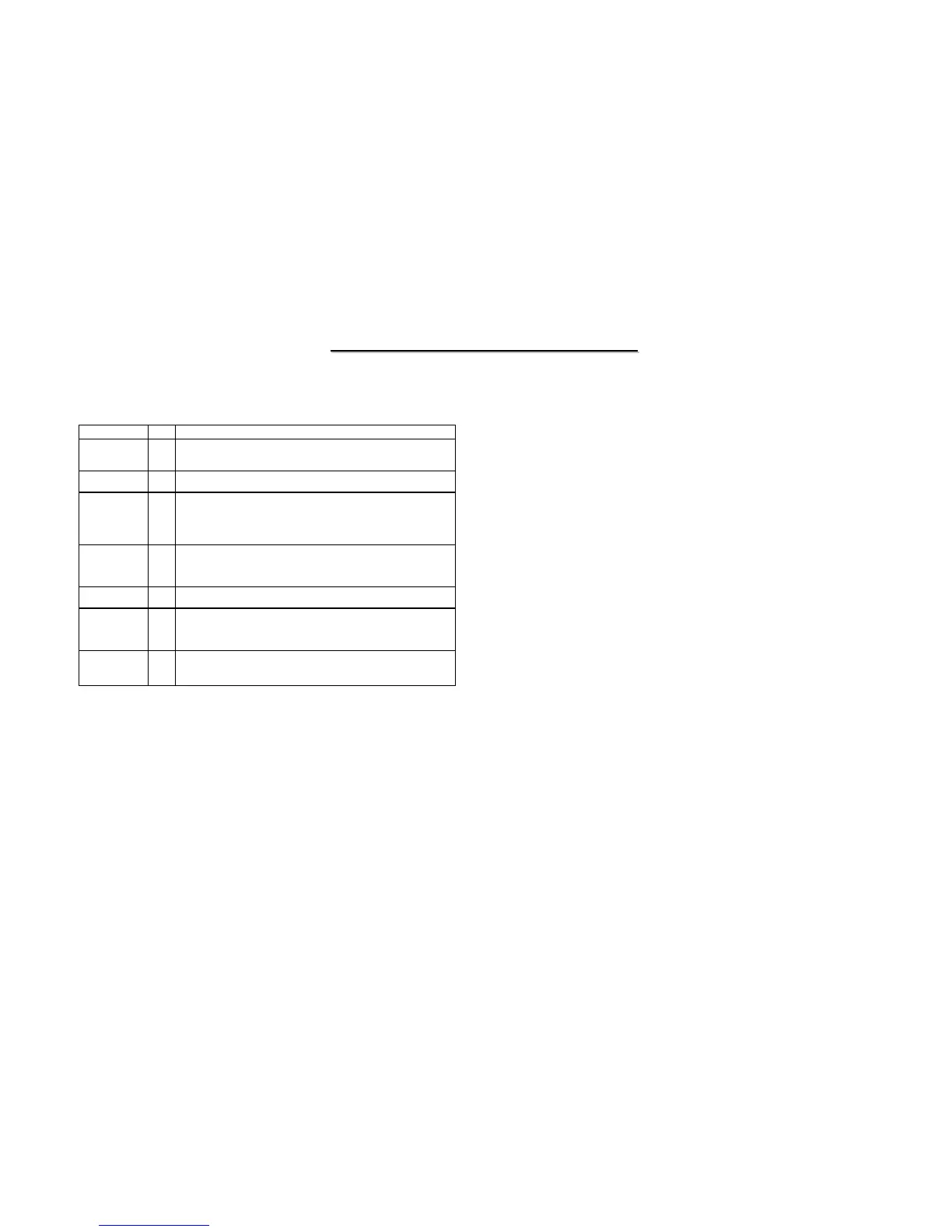

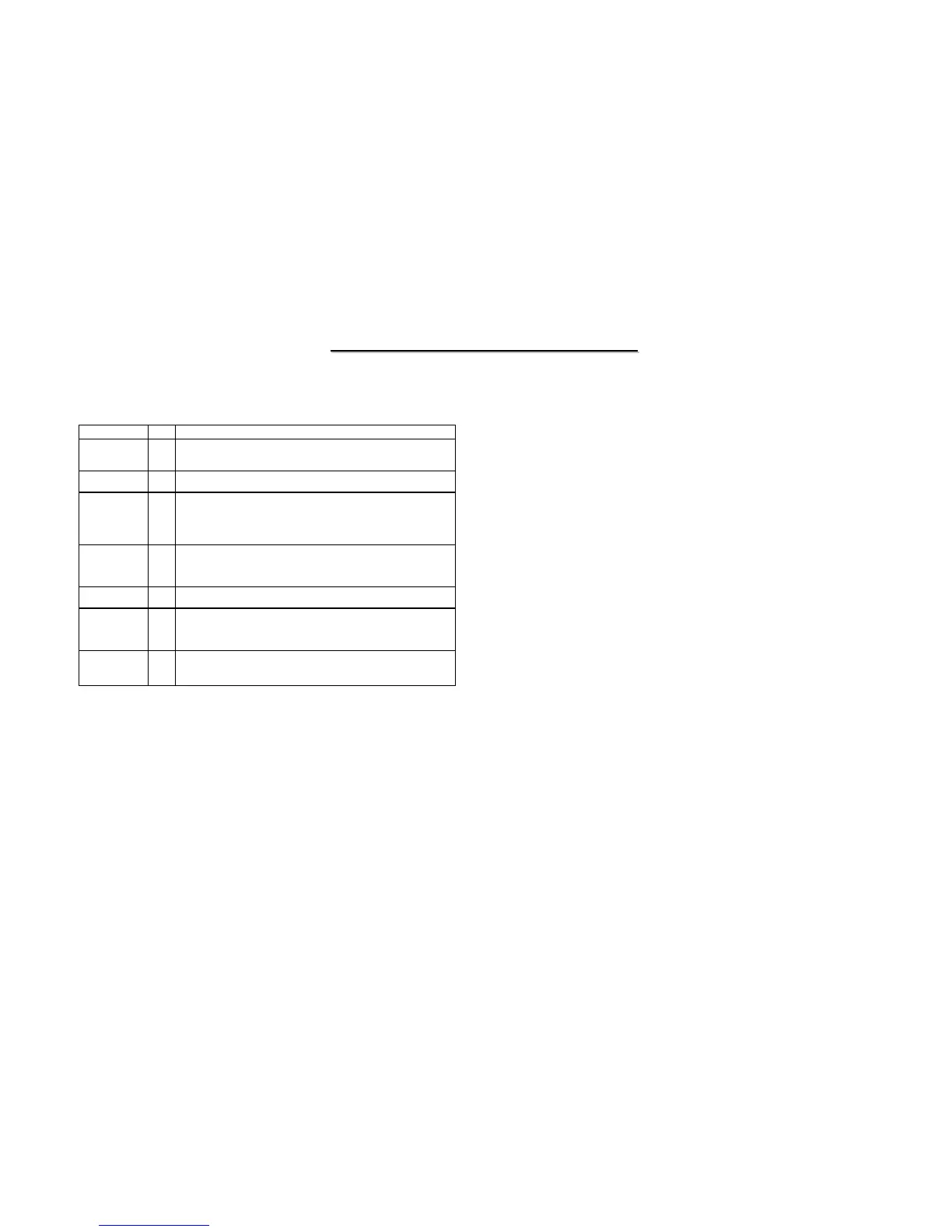

Name I/O Description

CPERR#

I/O CardBus parity error. CPERR# reports parity errors during CardBus

transactions, except during special cycles. It is driven low by a target two

clocks following that data when a parity error is detected.

CREQ#

I CardBus request. CREQ# indicates to the arbiter that the CardBus PC Card

desires use of the CardBus bus as an initiator.

CSERR#

I CardBus system error. CSERR# reports address parity errors and other

system errors that could lead to catastrophic results. CSERR# is driven by

the card synchronous to CCLK, but deasserted by a weak pullup, and may

take several CCLK periods. The PCI1410 can report CSERR# to the system

by assertion of SERR# on the PCI interface.

CSTOP#

I/O CardBus stop. CSTOP# is driven by a CardBus target to request the initiator

to stop the current CardBus transaction. CSTOP# is used for target

disconnects, and is commonly asserted by target devices that do not support

burst data transfers.

CSTSCHG

I CardBus status change. CSTSCHG alerts the system to a change in the

card’s status, and is used as a wake-up mechanism.

CTRDY#

I/O CardBus target ready. CTRDY# indicates the CardBus target’s ability to

complete the current data phase of the transaction. A data phase is

completed on a rising edge of CCLK, when both CIRDY# and CTRDY#

are asserted; until this time, wait states are inserted.

CVS1

CVS2

I/O CardBus voltage sense 1 and CardBus voltage sense 2. CVS1 and CVS2 are

used in conjunction with CCD1# and CCD2# to identify card insertion and

interrogate cards to determine the operating voltage and card type.

Loading...

Loading...