128

8575

8575

N/B Maintenance

N/B Maintenance

5.6 uPD72872 IEEE1394 Controller

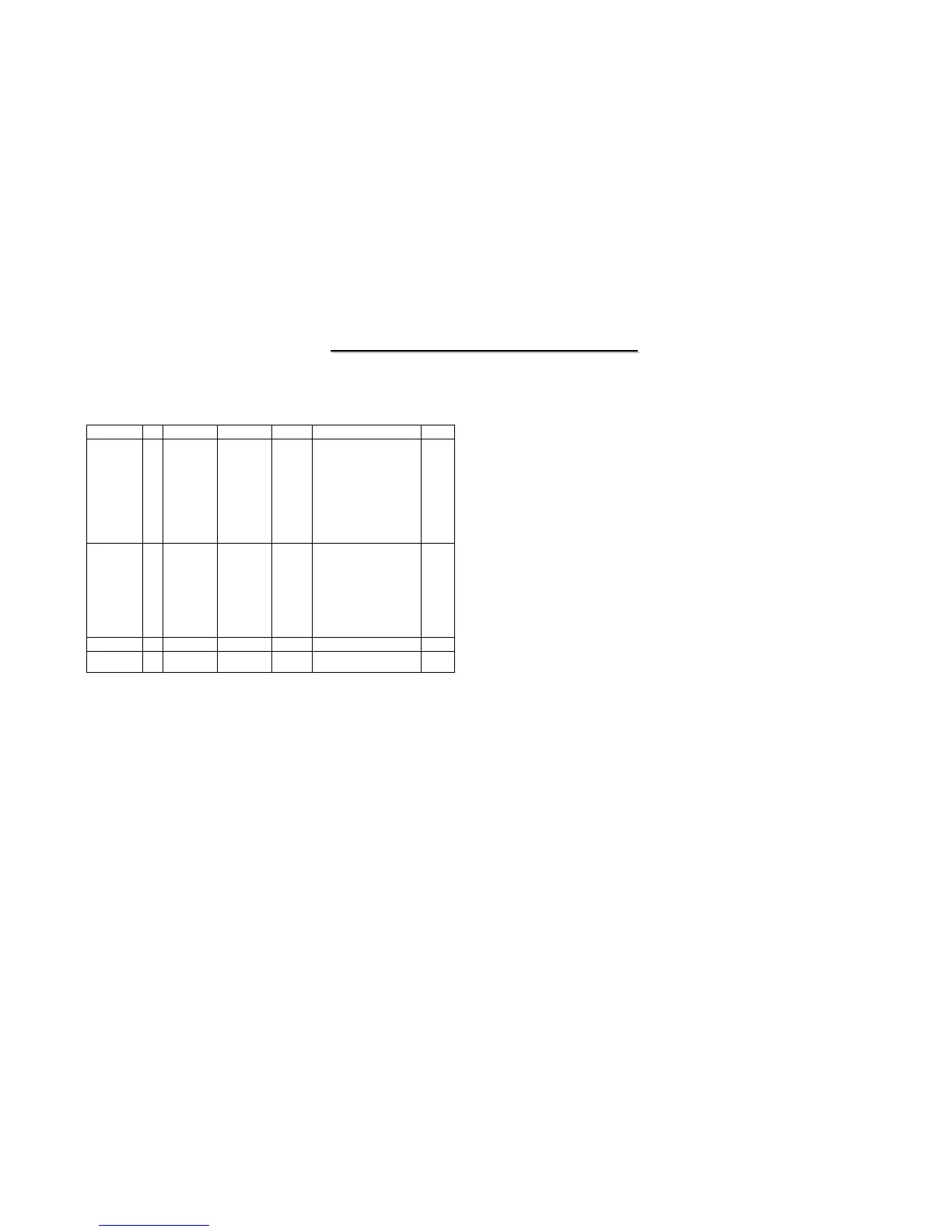

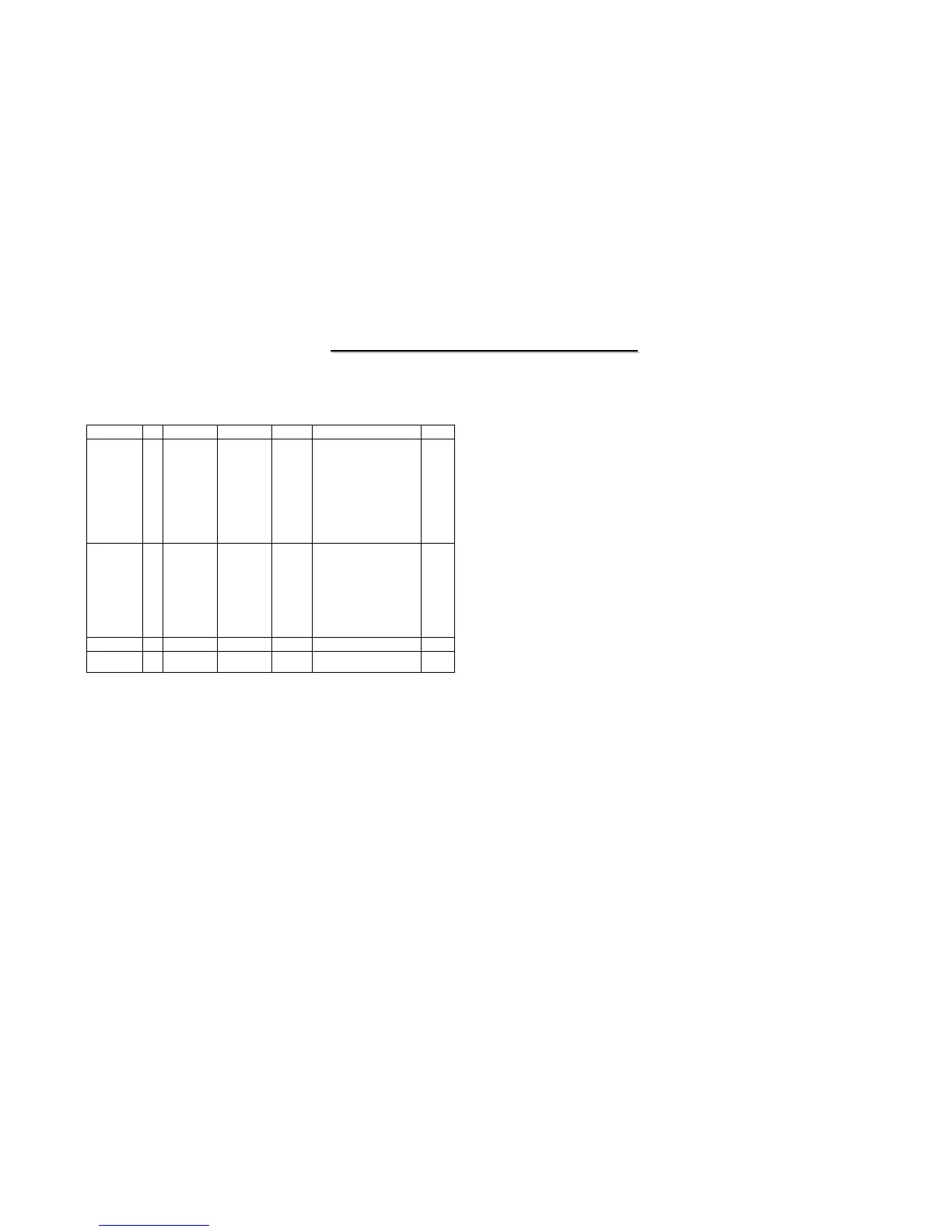

Name I/O PIN NO. IOL Volts(V) Function Block*

PERR

I/O 41 PCI/Cardbus 5/3.3 Parity Error is used for

reporting data parity errors

during all PCI transactions,

except a Special Cycle.

It is an output when

AD0-AD31 and PAR are

both inputs. It is an input

when AD0-AD31 and PAR

are both outputs.

Link

SERR

O 42 PCI/Cardbus 5/3.3 System Error is used for

reporting address parity

errors, data parity errors

during the Special Cycle, or

any other system error

where the effect can be

catastrophic. When reporting

address parity errors, it is an

output.

Link

PRST

I 5 - 5/3.3 Reset PCI reset Link

PCLK

I 6 - 5/3.3 PCI Clock 33 MHz system

bus clock.

Link

Remark *: If the Link pin is pulled up, it should be connected to L_VDD.

Loading...

Loading...