69

8575

8575

N/B Maintenance

N/B Maintenance

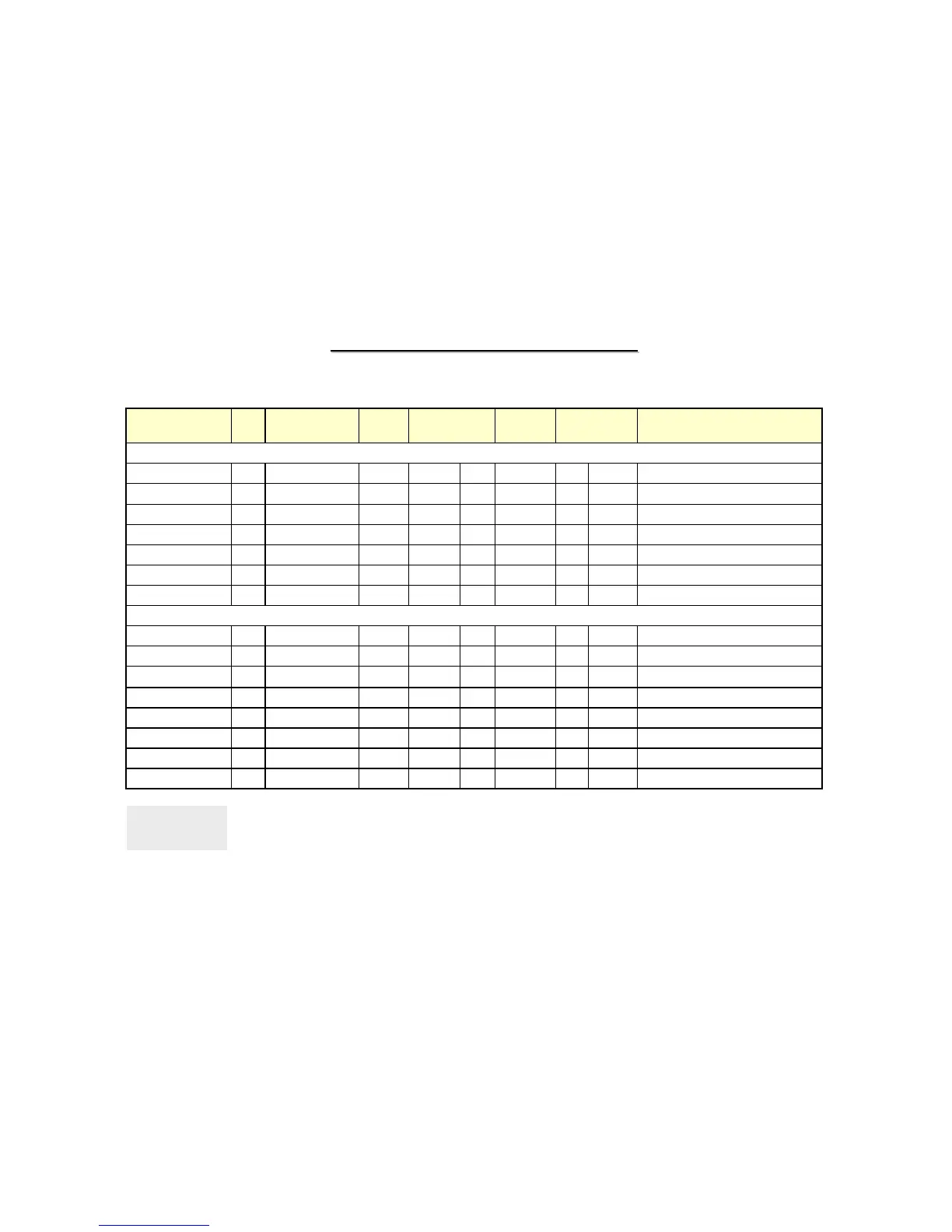

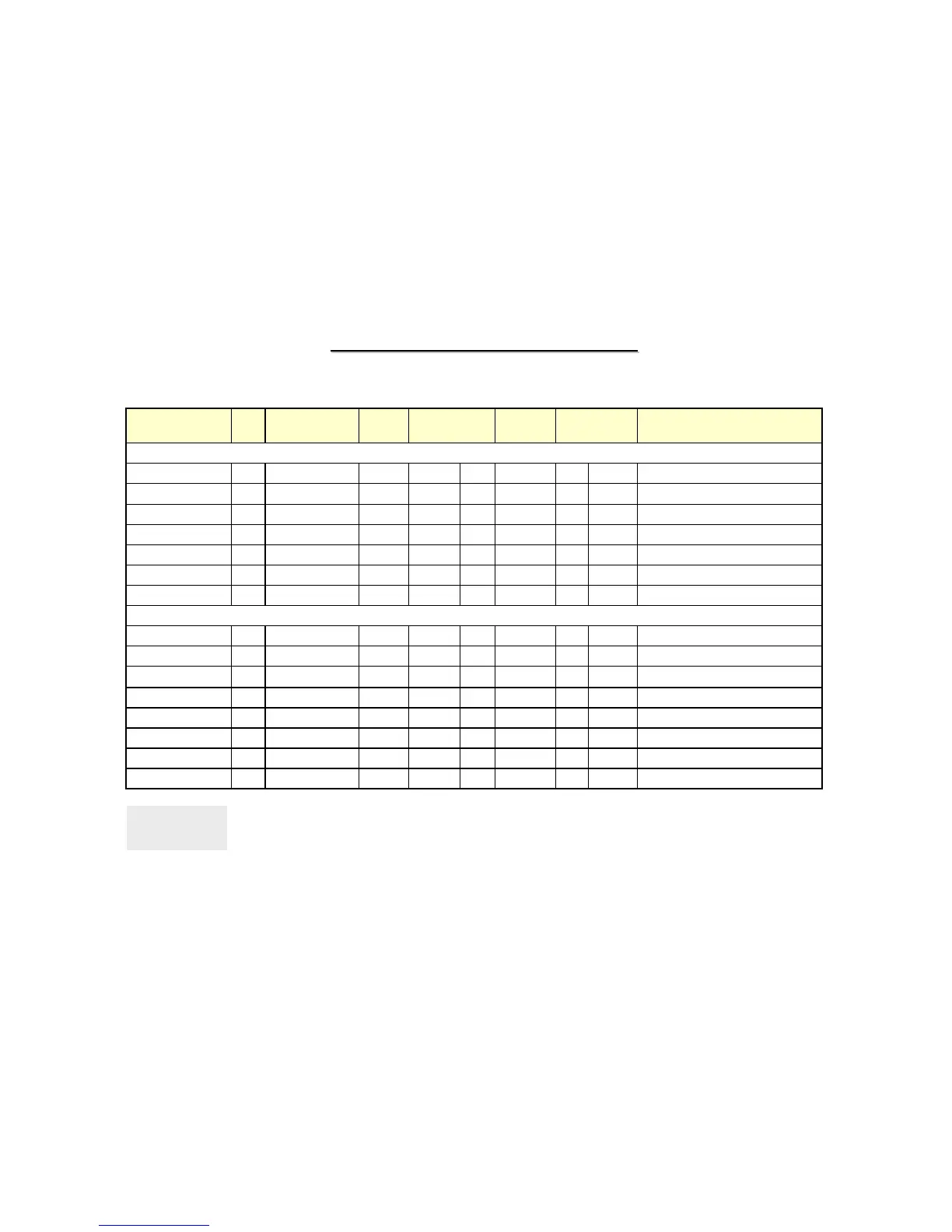

SM BUS clock need pull high 5→3VKeepI/OI/OI/OT↑BAT DATA16P97/WAIT/SDA

Read H8 send A20gate statusTIIIT↑ENABKL17P96/0

need pull highKeepI/OI/OI/OT↑H8/T DATA18P95/AS

need pull highKeepI/OI/OI/OT↑M DATA19P94/WR

need pull highKeepI/OI/OI/OT↑K/M DATA22P93/RD

need pull high

SM BUS clock need pull high 5→3V

CPU A20gate

KeepI/OI/OI/OT↑K/M CLK25P90/IRQ2/ESC2

Port 9 TTL input voltage (input high min=2V, input low max=0.8V)

KeepIIITISA SA293P80/HA0

need pull high

need pull high

IO port 62/66 chip select

ISA I/O write

ISA I/O read#

IO port 60/64 chip select

Function

Keep

Keep

Keep

Keep

Keep

Keep

Keep

Keep H

STANDBY

I/O

I/O

I/O

I

I

I

I

O

I/O

I/O

I/O

I

I

I

I

O

ON

I/O

I/O

I/O

I

I

I

I

O

After

RESET/OFF

T↑

T↑

T↑

T

T

T

T

T

During

RESET

H8/T CLK

M CLK

BAT CLK

H8 MCCS#

ISA IOW#

ISA IOR#

H8 KBCS#

X(H8 A20GATE)

H8 Pin

Definitions

23

24

99

98

97

96

95

94

Pin

P92/IRQ0

P91/IRQ1/EIOW

P86/IRQ5/SCK1

P85/IRQ4/RXD1

P84/IRQ2/TXD1

P83/IOR

P82/CS1

P81/GA20

Port 8 TTL input voltage (input high min=2V, input low max=0.8V)

Name

↑ Pull High

↓ Pull Low

5→3V Level shift

Continue to previous

Loading...

Loading...