On-Chip Cache Memories

MOTOROLA

MC68030 USER’S MANUAL

6-5

When enabled, the instruction cache is used to store instruction prefetches (instruction

words and extension words) as they are requested by the CPU. Instruction prefetches are

normally requested from sequential memory addresses except when a change of program

flow occurs (e.g., a branch taken) or when an instruction is executed that can modify the

status register, in which cases the instruction pipe is automatically flushed and refilled. The

output signal REFILL

indicates this condition. For more information on the operation of this

signal, refer to

Section 12 Applications Information

.

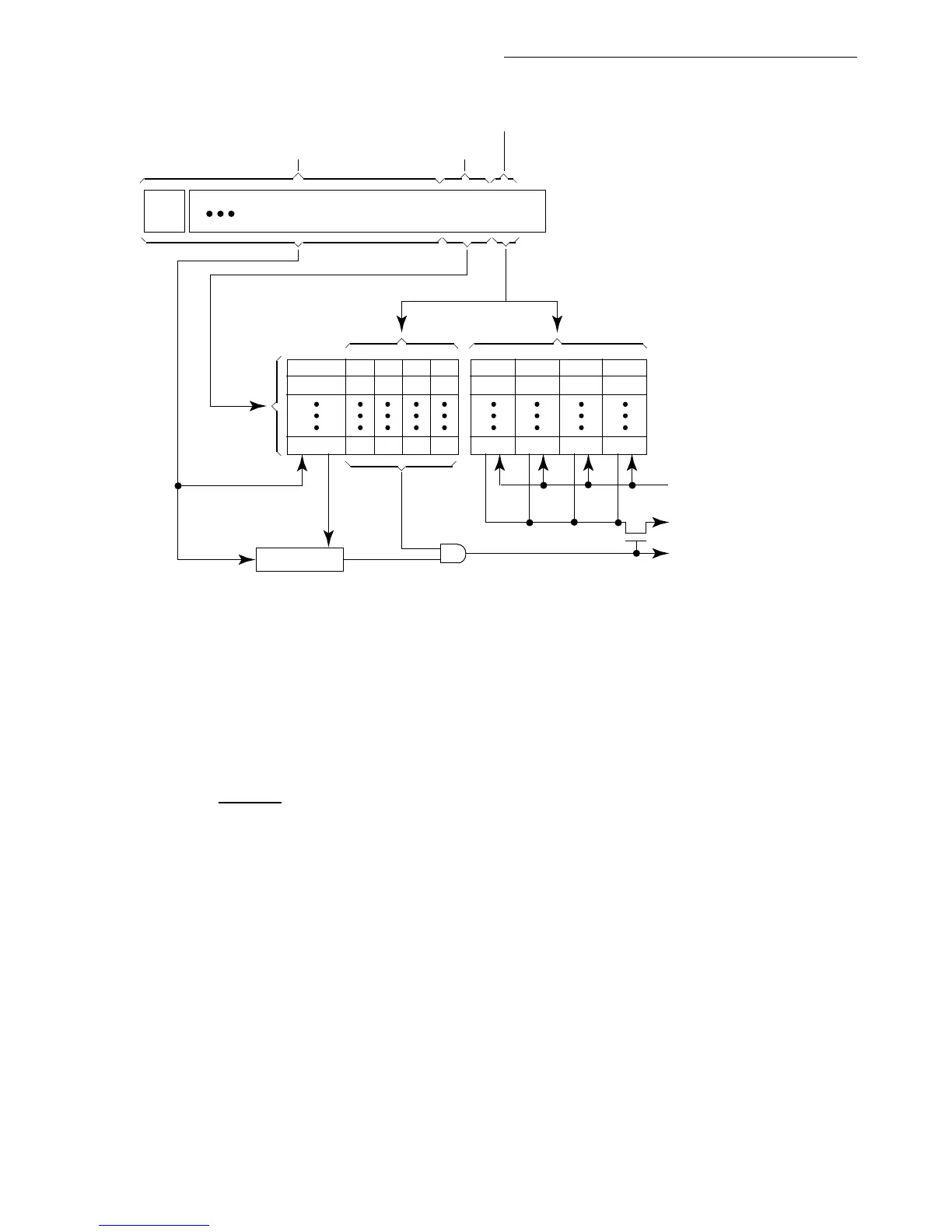

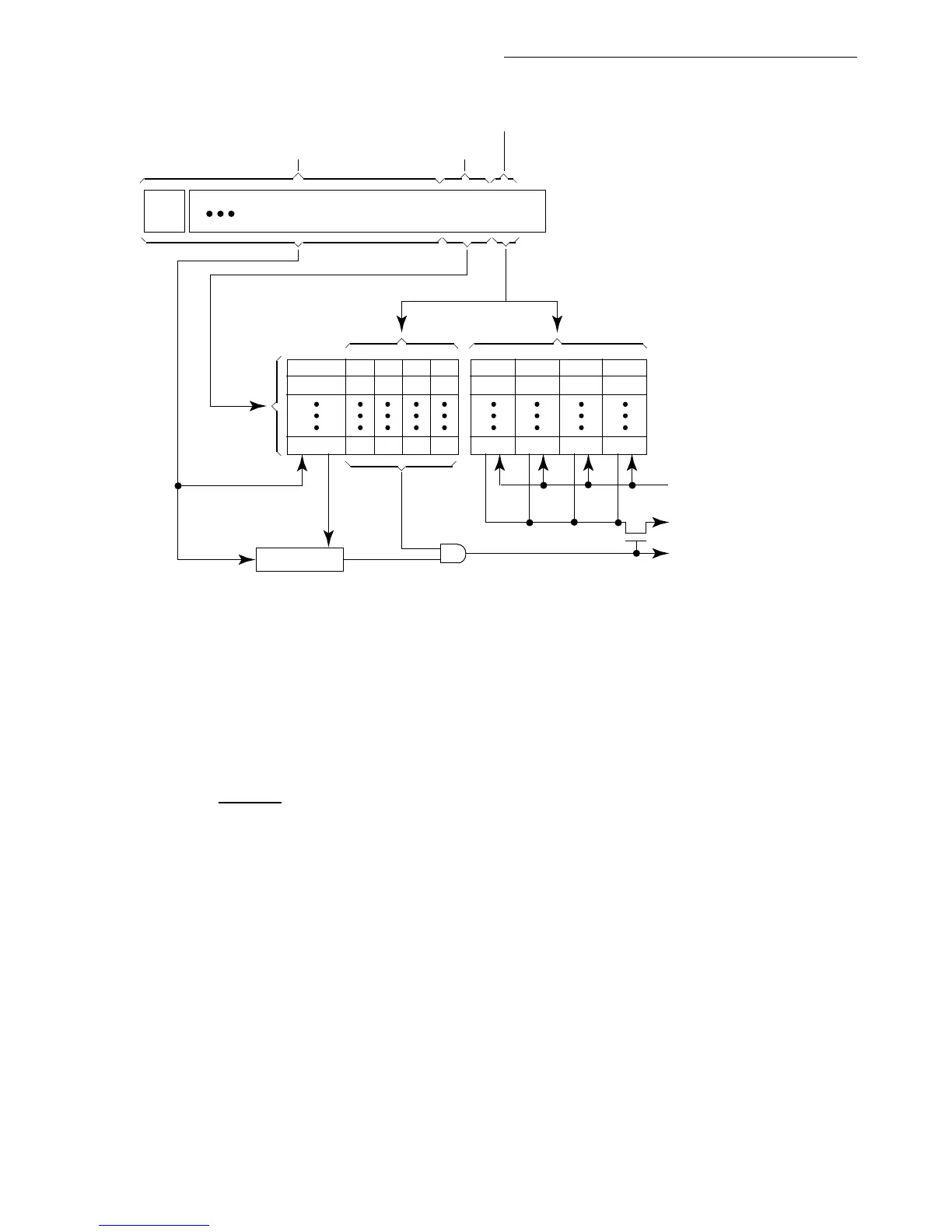

In the instruction cache, each of the 16 lines has a tag consisting of the 24 most significant

logical address bits, the FC2 function code bit (used to distinguish between user and

supervisor accesses), and the four valid bits (one corresponding to each long word). Refer

to Figure 6-2 for the instruction cache organization. Address bits A7–A4 select one of 16

lines and its associated tag. The comparator compares the address and function code bits

in the selected tag with address bits A31–A8 and FC2 from the internal prefetch request to

determine if the requested word is in the cache. A cache hit occurs when there is a tag match

and the corresponding valid bit (selected by A3–A2) is set. On a cache hit, the word selected

by address bit A1 is supplied to the instruction pipe.

When the address and function code bits do not match or the requested entry is not valid, a

miss occurs. The bus controller initiates a long-word prefetch operation for the required

Figure 6-2. On-Chip Instruction Cache Organization

F F F

CCC 3 222211111111110000000000

210 1 32 01 987 65432109876543210

COMPARATOR

TAG

1 OF 16

SELECT

VALID

TAG REPLACE

INDEX

TAG

LINE HIT

DATA FROM INSTRUCTION

CACHE DATA BUS

CACHE CONTROL LOGIC

V V VV

ACCESS ADDRESS

DATA TO INSTRUCTION

CACHE HOLDING REGISTER

ENTRY HIT

A

LONG-WORD

SELECT

CACHE SIZE = 64 (LONG WORDS)

LINE SIZE = 4 (LONG WORDS)

SET SIZE = 1

AAAAAAAAAAAAAAAAAAAAAAAA

Loading...

Loading...