Instruction Set Summary

3-12 MC68030 USER’S MANUAL MOTOROLA

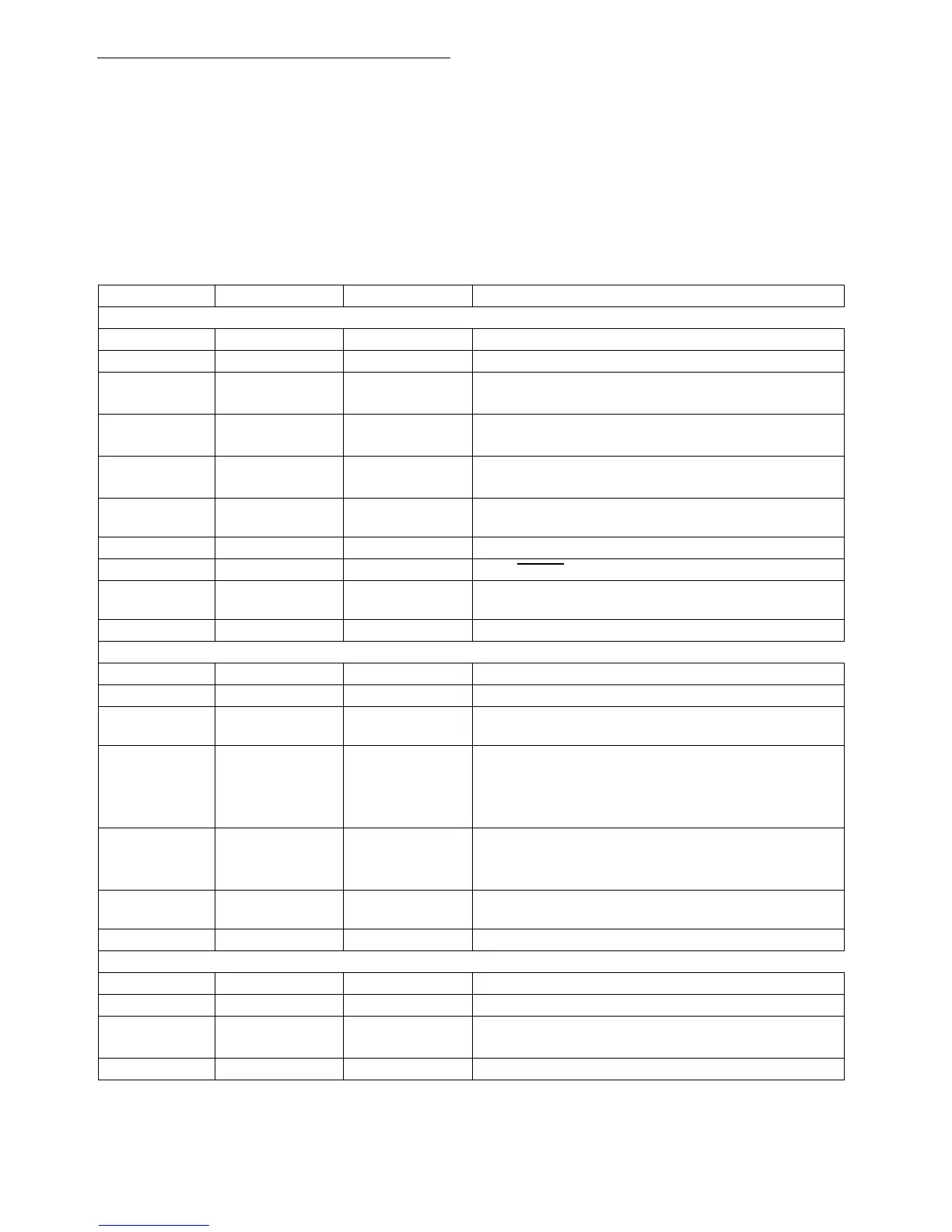

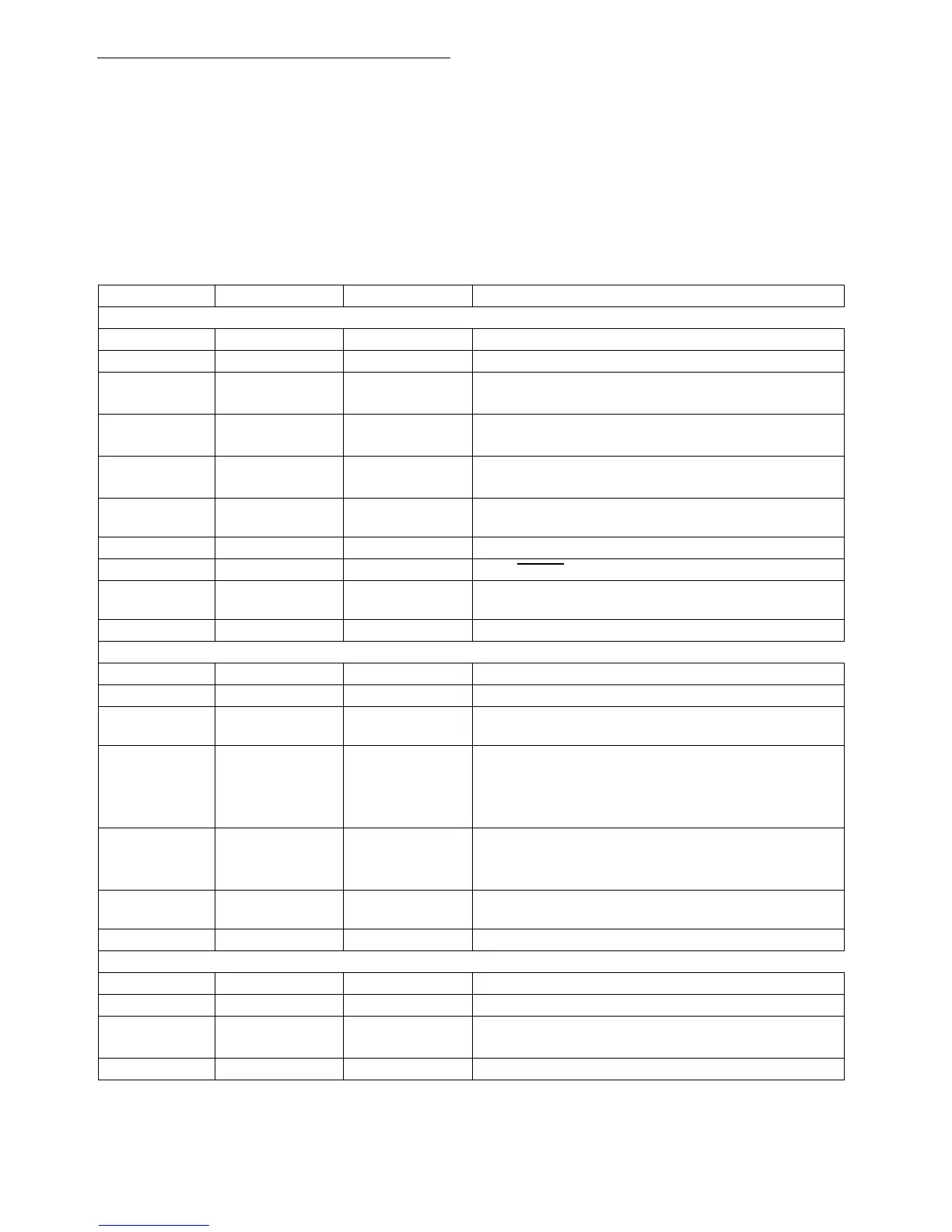

3.2.9 System Control Instructions

Privileged instructions, trapping instructions, and instructions that use or modify the

condition code register (CCR) provide system control operations. Table 3–9 summarizes

these instructions. The TRAPcc instruction uses the same conditional tests as the

corresponding program control instructions. All of these instructions cause the processor to

flush the instruction pipe.

Table 3-9. System Control Operations

Instruction Operand Syntax Operand Size Operation

Privileged

ANDI #〈data〉,SR 16 immediate data Λ SR → SR

EORI #〈data〉,SR 16 immediate data x SR → SR

MOVE 〈ea〉,SR

SR,〈ea〉

16

16

source → SR

SR → destination

MOVE USP,An

An,USP

32

32

USP → An

An → USP

MOVEC Rc,Rn

Rn,Rc

32

32

Rc → Rn

Rn → Rc

MOVES Rn, 〈ea〉

〈ea〉,Rn

8, 16, 32 Rn → destination using DFC

source using SFC → Rn

ORI #〈data〉,SR 16 immediate data V SR → SR

RESET none none assert RESET

line

RTE none none (SP) → SR; SP + 2 → SP; (SP) → PC; SP + 4 → SP;

Restore stack according to format

STOP #〈data〉 16 immediate data → SR; STOP

Trap Generating

BKPT #〈data〉 none run breakpoint cycle, then trap as illegal instruction

CHK 〈ea〉,Dn 16, 32 if Dn < 0 or Dn > (ea), then CHK exception

CHK2 〈ea〉,Rn 8, 16, 32 if Rn < -lower bound or Rn > -upper bound, then CHK

exception

ILLEGAL none none SSP — 2 → SSP; Vector Offset→ (SSP);

SSP — 4 → SSP; PC→ (SSP);

SSP — 2 → SSP; SR→ (SSP);

Illegal Instruction Vector Address → PC

TRAP #〈data〉 none SSP — 2 → SSP; Format and Vector Offset→(SSP)

SSP — 4 → SSP; PC→(SSP); SSP — 2 → SSP;

SR→(SSP); Vector Address → PC

TRAPcc none

#〈data〉

none

16, 32

if cc true, then TRAP exception

TRAPV none none if V, then take overflow TRAP exception

Condition Code Register

ANDI #〈data〉,CCR 8 immediate data Λ CCR → CCR

EORI #〈data〉,CCR 8 immediate data ⊕ CCR → CCR

MOVE 〈ea〉,CCR

CCR,〈ea〉

16

16

source → CCR

CCR → destination

ORI #〈data〉,CCR 8 immediate data V CCR → CCR

Loading...

Loading...