Instruction Set Summary

MOTOROLA MC68030 USER’S MANUAL 3-13

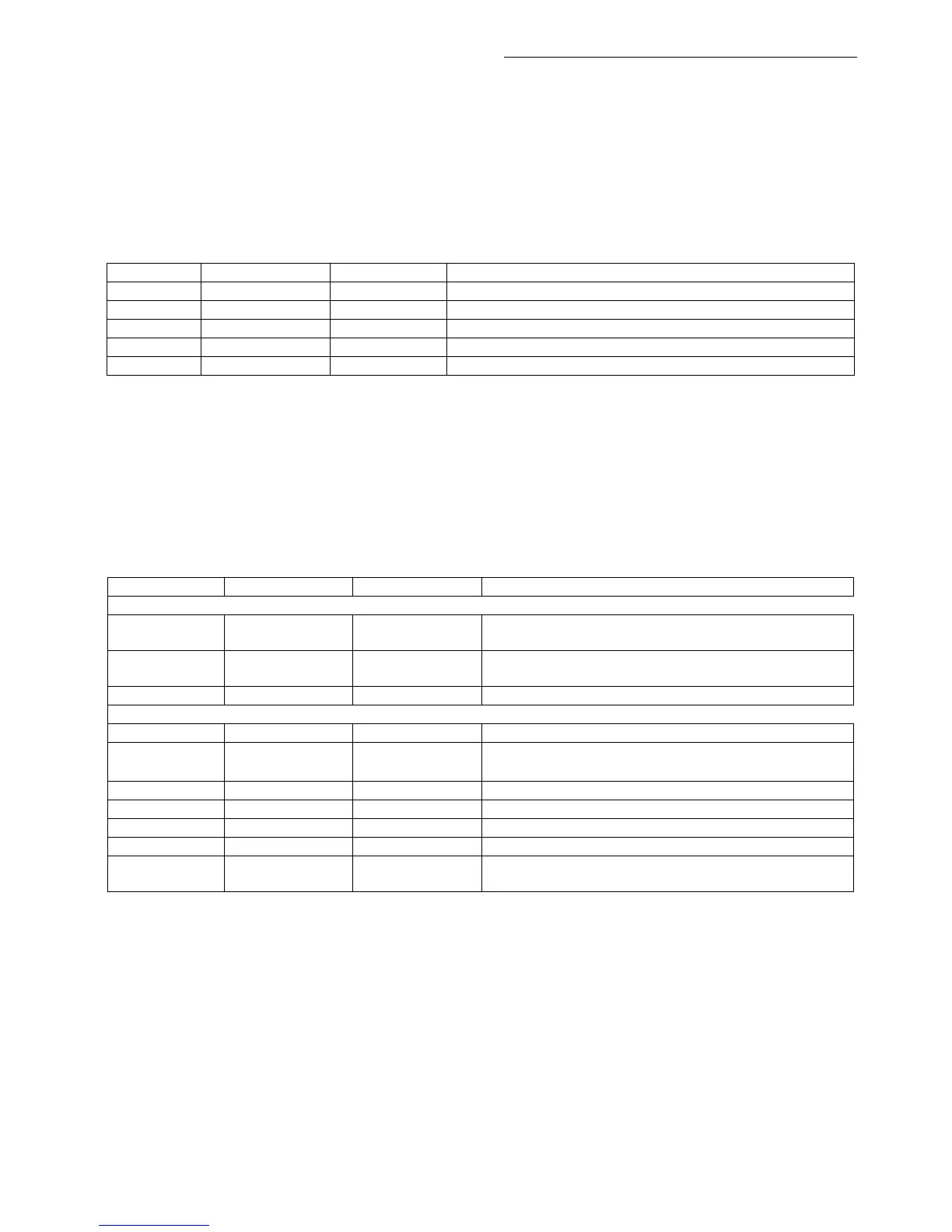

3.2.10 Memory Management Unit Instructions

The PFLUSH instructions flush the address translation caches (ATCs) and can optionally

select only nonglobal entries for flushing. PTEST performs a search of the address

translation tables, storing results in the MMU status register and loading the entry into the

ATC. Table 3–10 summarizes these instructions.

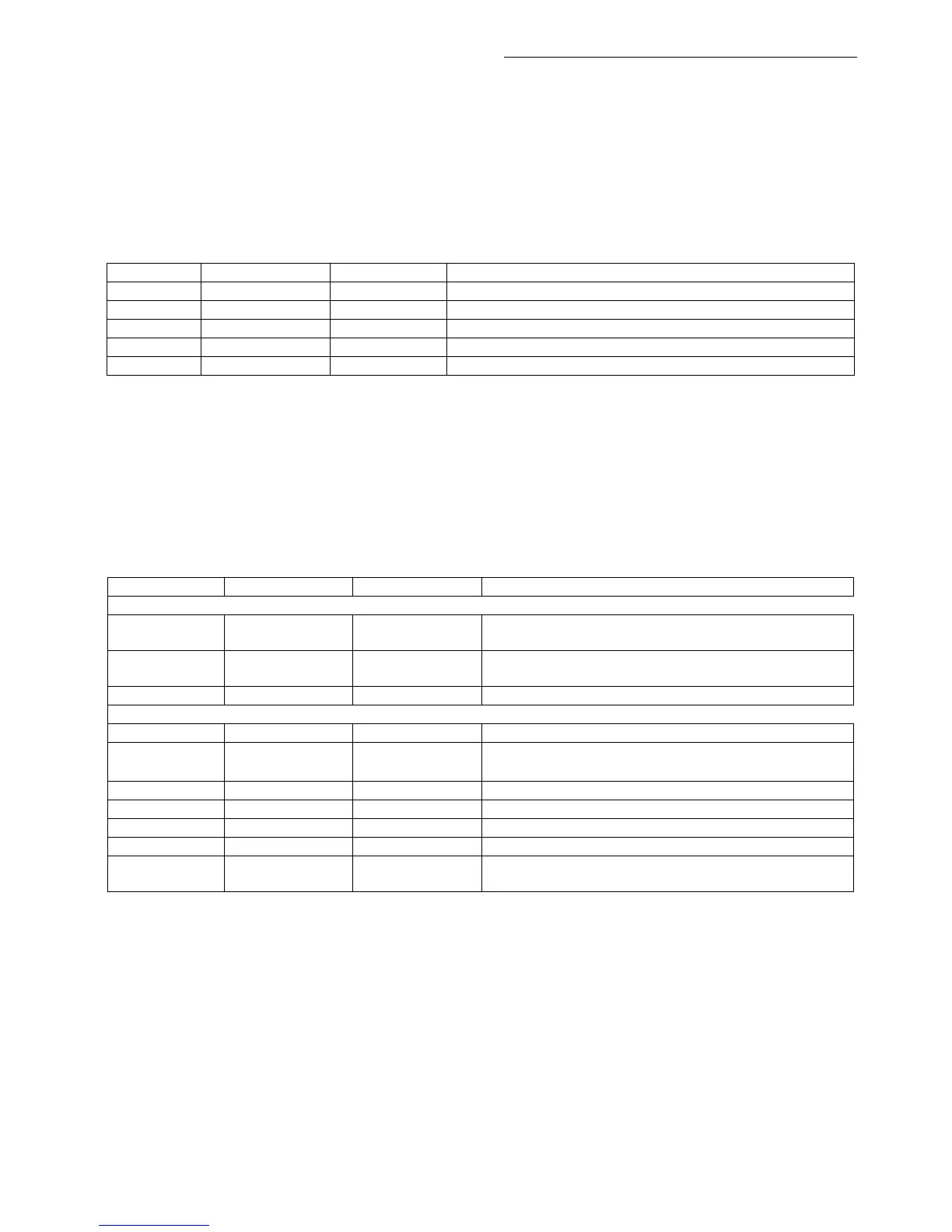

3.2.11 Multiprocessor Instructions

The TAS, CAS, and CAS2 instructions coordinate the operations of processors in

multiprocessing systems. These instructions use read-modify-write bus cycles to ensure

uninterrupted updating of memory. Coprocessor instructions control the coprocessor

operations. Table 3–11 lists these instructions.

Table 3-10. MMU Instructions

Instruction Operand Syntax Operand Size Operation

PFLUSHA none none Invalidate all ATC entries

PFLUSHA.N none none Invalidate all nonglobal ATC entries

PFLUSH (An) none Invalidate ATC entries at effective address

PFLUSH.N (An) none Invalidate nonglobal ATC entries at effective address

PTEST (An) none Information about logical address → MMU status register

Table 3-11. Multiprocessor Operations (Read-Modify-Write)

Instruction Operand Syntax Operand Size Operation

Read-Modify-Write

CAS Dc,Du,〈ea〉 8, 16, 32 destination — Dc → CC; if Z then Du → destination

else destination→Dc

CAS2 Dc1:Dc2,Du1:Du2,(

Rn):(Rn)

8, 16, 32 dual operand CAS

TAS 〈ea〉 8 destination — 0; set condition codes; 1 → destination [7]

Coprocessor

cpBcc 〈label〉 16, 32 if cpcc true, then PC + d → PC

cpDBcc label,Dn 16 if cpcc false then Dn –1 → Dn

if Dn ≠ –1, then PC + d → PC

cpGEN User Defined User Defined operand → coprocessor

cpRESTORE 〈ea〉 none restore coprocessor state from 〈ea〉

cpSAVE 〈ea〉 none save coprocessor state at 〈ea〉

cpScc 〈ea〉 8 if cpcc true, then 1's → destination; else 0's → destination

cpTRAPcc none

#〈data〉

none

16, 32

if cpc true, then TRAPcc exception

Loading...

Loading...