Bus Operation

MOTOROLA

MC68030 USER’S MANUAL

7-9

Table 7-4 lists the bytes required on the data bus for read cycles that are cachable. The

entries shown as OPn are portions of the requested operand that are read or written during

that bus cycle and are defined by SIZ0, SIZ1, A0, and A1 for the bus cycle. The PRn and

the Nn bytes correspond to the previous and next bytes in memory, respectively, that must

be valid on the data bus for the specified port size (long word or word) so that the internal

caches operate correctly. (For cachable accesses, the MC68030 assumes that all portions

of the data bus for a given port size are valid.) This same table applies to noncachable read

cycles except that the bytes labeled PRn and Nn are not required and can be replaced by

“don't cares”.

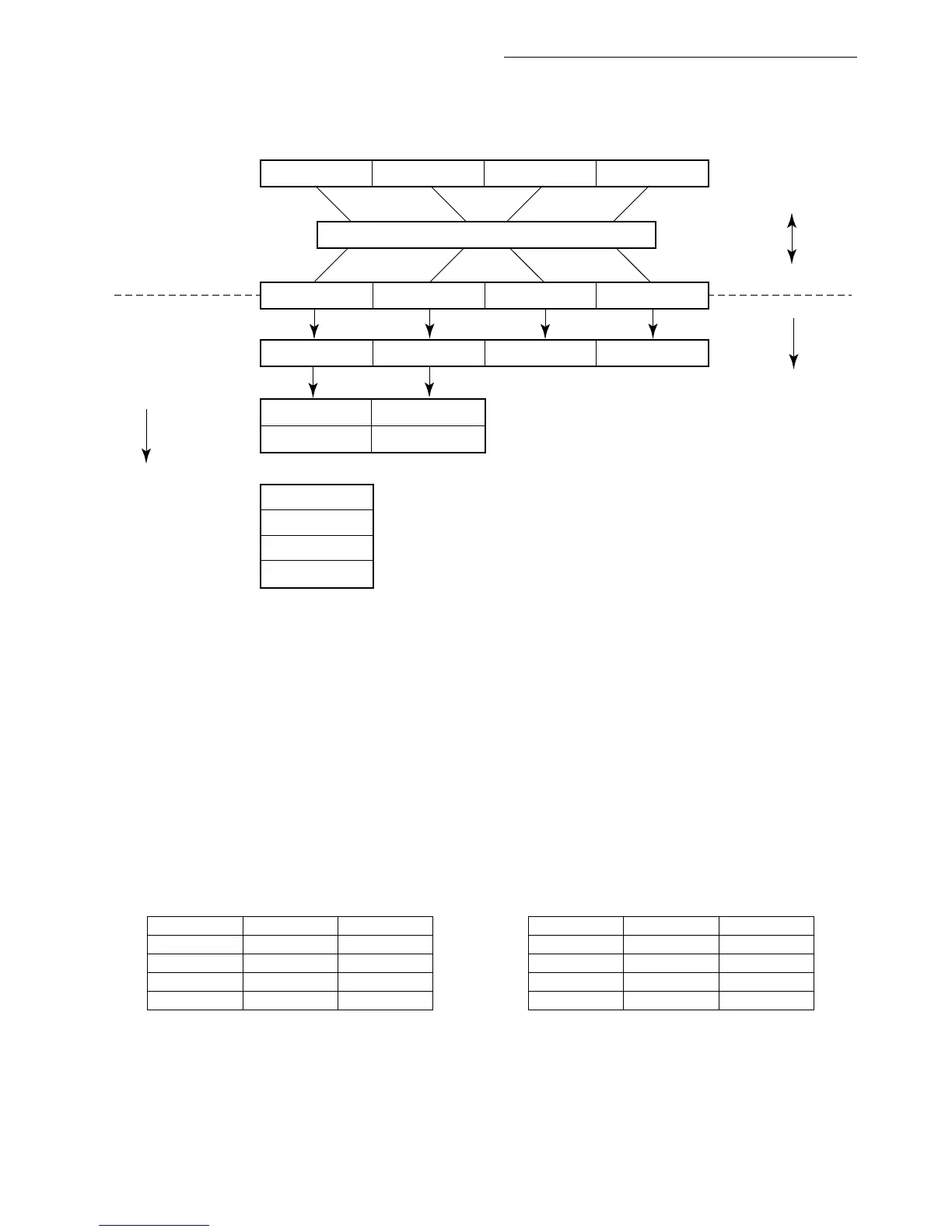

Figure 7-4. MC68030 Interface to Various Port Sizes

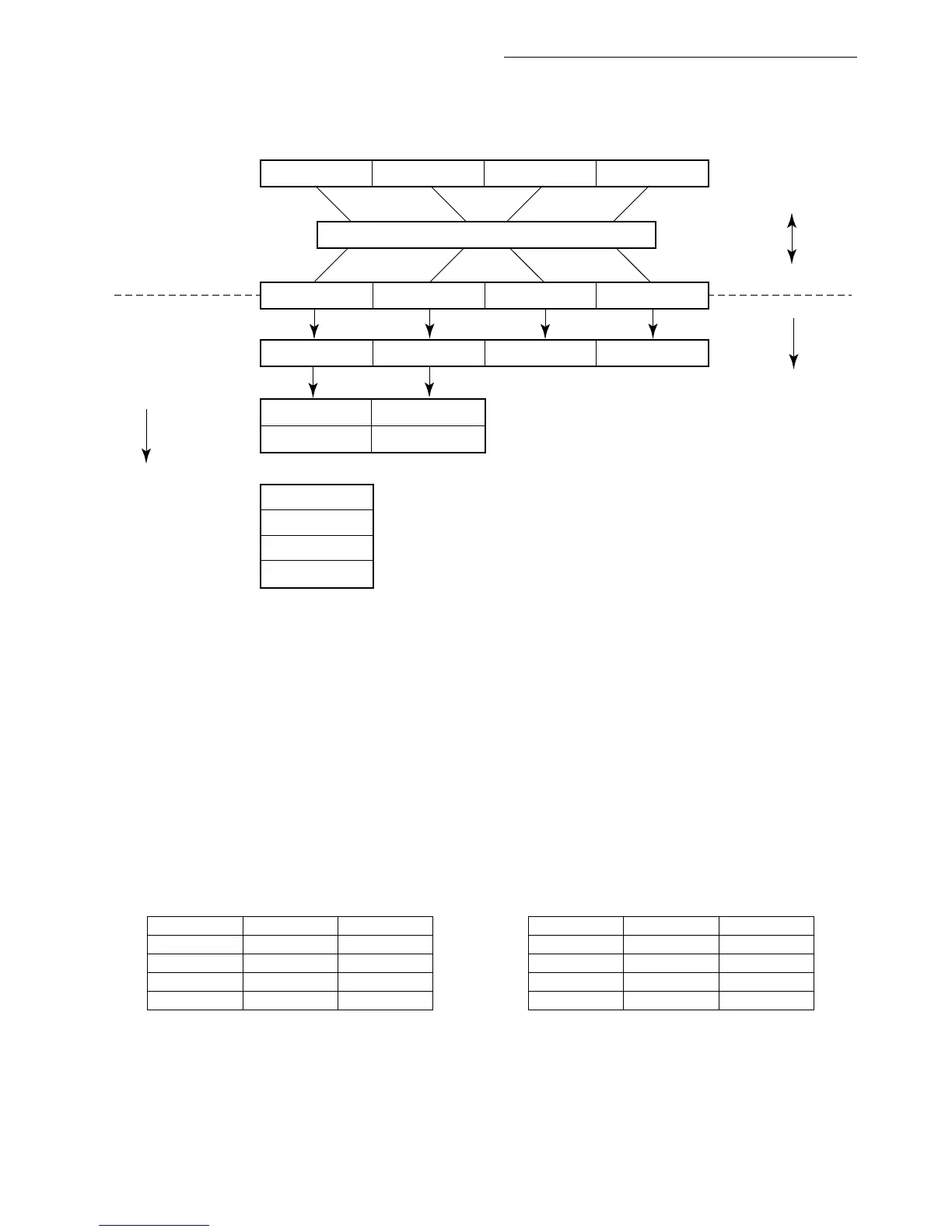

Table 7-2. Size Signal

Encoding

Table 7-3. Address Offset

Encodings

SIZ1 SIZ0 Size A1 A0 Offset

0 1 Byte 0 0 +0 Bytes

1 0 Word 0 1 +1 Byte

1 1 3 Bytes 1 0 +2 Bytes

0 0 Long Word 1 1 +3 Bytes

0123

ROUTING AND DUPLICATION

BYTE 0

BYTE 2

BYTE 1

BYTE 3

16-BIT PORT

REGISTER

MULTIPLEXER

EXTERNAL

DATA BUS

ADDRESS

xxxxxxxx0

xxxxxxxx0

2

INCREASING

MEMORY

ADDRESSES

D31- D24 D23-D16 D15-D8 D7-D0

BYTE 0 BYTE 1 BYTE 2 BYTE 3

BYTE 0

BYTE 1

BYTE 2

BYTE 3

8-BIT PORT

2

3

1

xxxxxxxx0

EXTERNAL BUS

INTERNAL TO

THE MC68EC030

32-BIT PORT

OP0 OP1 OP2 OP3

-

ab

Loading...

Loading...