Bus Operation

7-20

MC68030 USER’S MANUAL

MOTOROLA

Table 7-6 shows that the processor always prefetches instructions by reading a long word

from a long-word address (A1:A0=00), regardless of port size or alignment. When the

required instruction begins at an odd-word boundary, the processor attempts to fetch the

entire 32 bits and loads both words into the instruction cache, if possible, although the

second one is the required word. Even if the instruction access is not cached, the entire 32

bits are latched into an internal cache holding register from which the two instructions words

can subsequently be referenced. Refer to

Section 11 Instruction Execution Timing

for a

complete description of the cache holding register and pipeline operation.

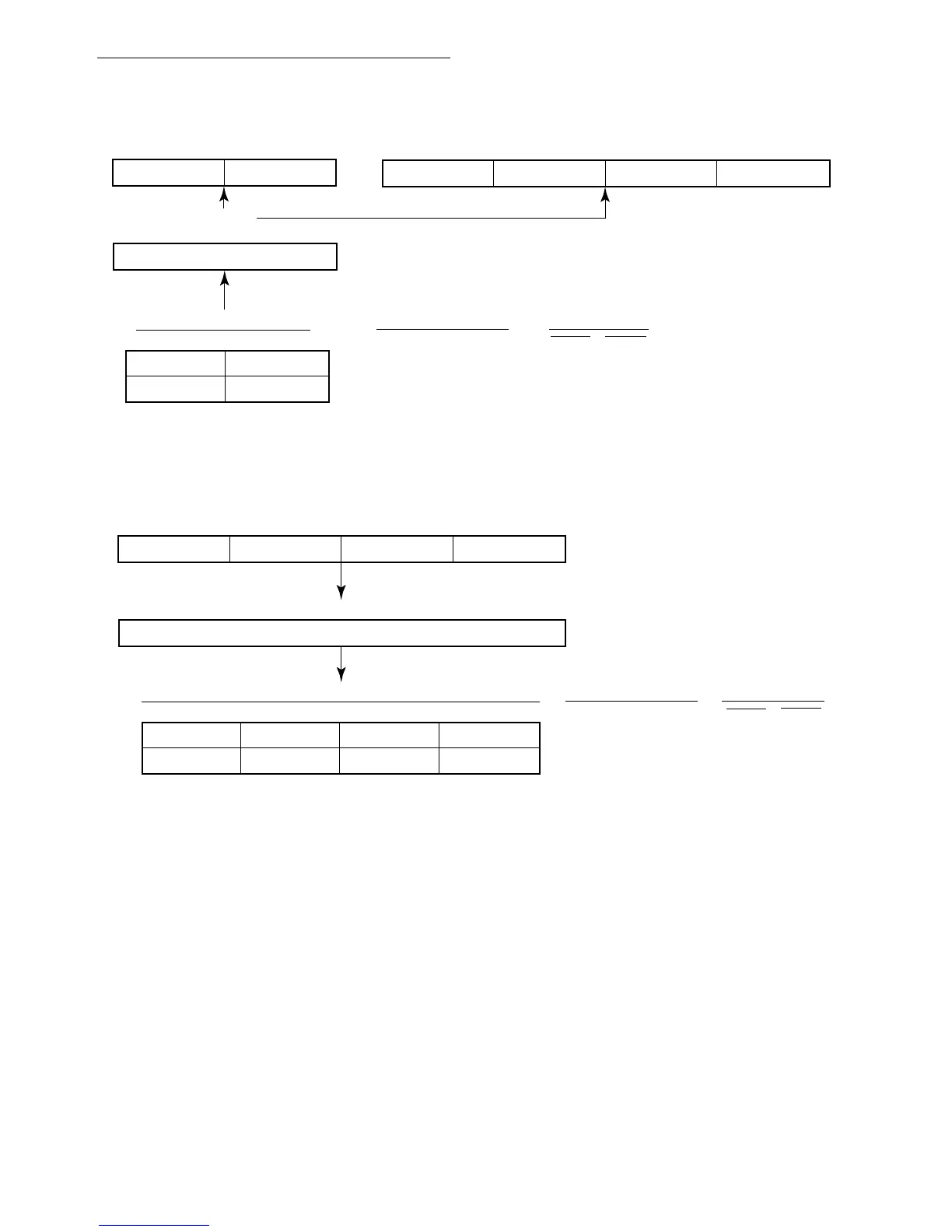

Figure 7-14. Example of Misaligned Cachable Word Transfer from Word Bus

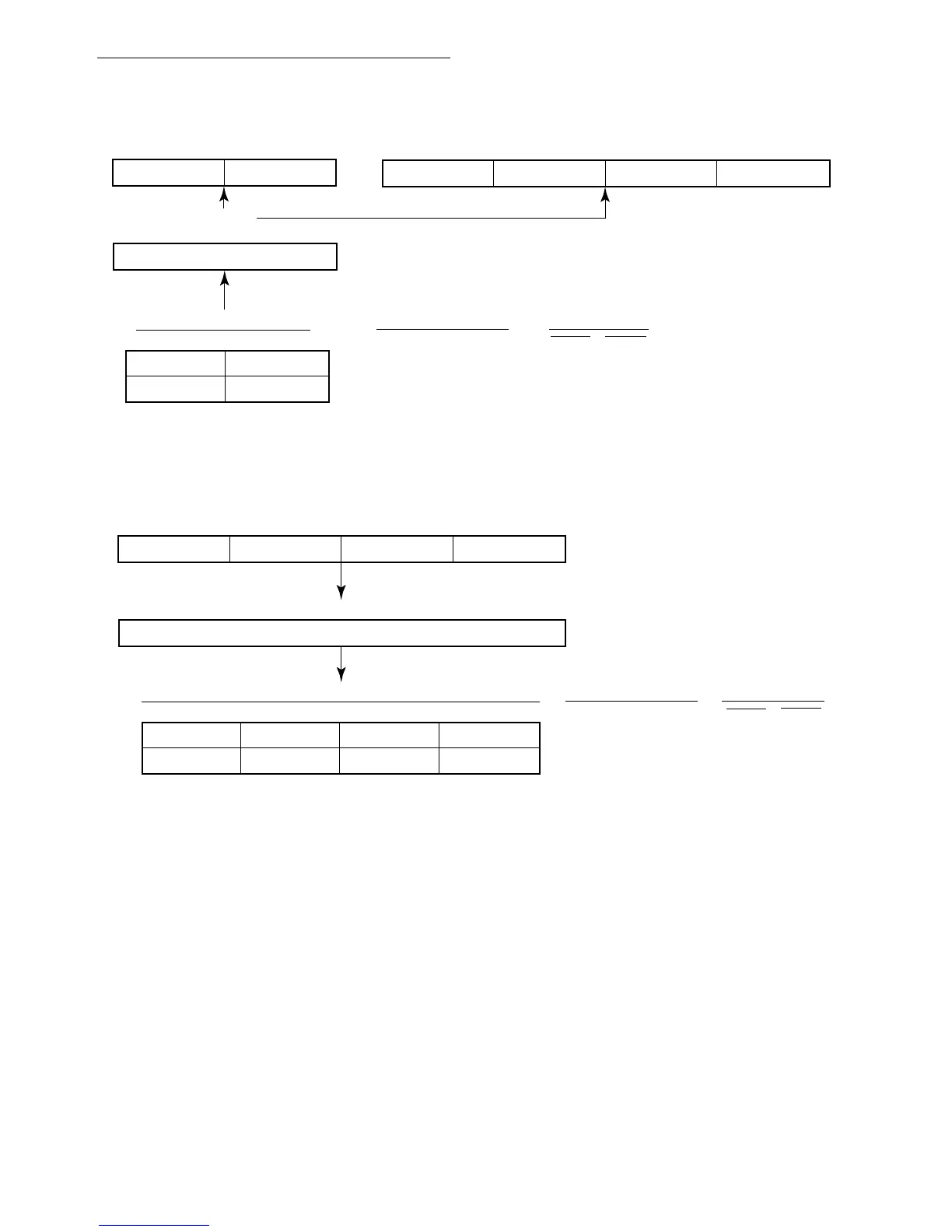

Figure 7-15. Misaligned Long-Word Transfer to Long-Word Port

MC68EC030

SIZ1 SIZ0 A2 A1

1 0 0 0 1

0 1 0 1 0

A0

MEMORY CONTROL

DSACK1 DSACK0

LH

LH

OP2 OP3

15

0

WORD OPERAND (REGISTER)

DATA BUS

D31 D16

WORD MEMORY

MSB LSB

XXX

OP3

OP2

XXX

PR OP2

31 0CACHE ENTRY

OP3 N

MC68EC030

SIZ1 SIZ0 A2 A1

0 0 0 1 1

1 1 1 0 0

A0

MEMORY CONTROL

DSACK1 DSACK0

L

LL

OP0 OP1

15 0LONG WORD OPERAND

DATA BUSD31 D0

LONG WORD MEMORY

MSB UMB

XXX

OP1 OP2

XXX XXX

OP2 OP3

OP3

OP0

XXX

LMB LSB

L

Loading...

Loading...