Bus Operation

MOTOROLA MC68030 USER’S MANUAL 7-39

State 0

The write cycle starts in S0. The processor drives ECS

low, indicating the beginning of

an external cycle. When the cycle is the first external cycle of a write operation, OCS

is

driven low at the same time. During S0, the processor places a valid address on A0–A31

and valid function codes on FC0–FC2. The function codes select the address space for

the cycle. The processor drives R/W low for a write cycle. SIZ0–SIZ1 become valid,

indicating the number of bytes to be transferred. CIOUT

also becomes valid, indicating

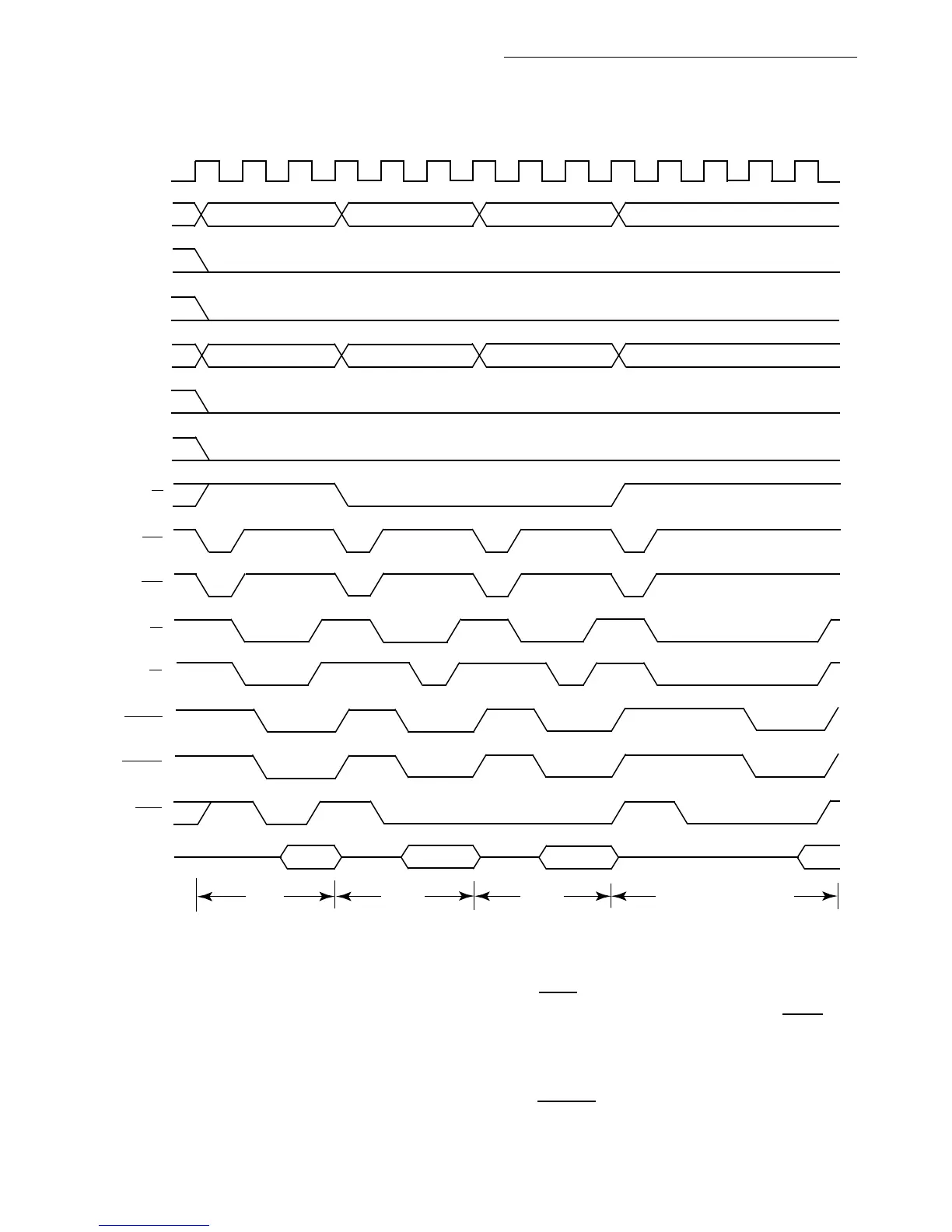

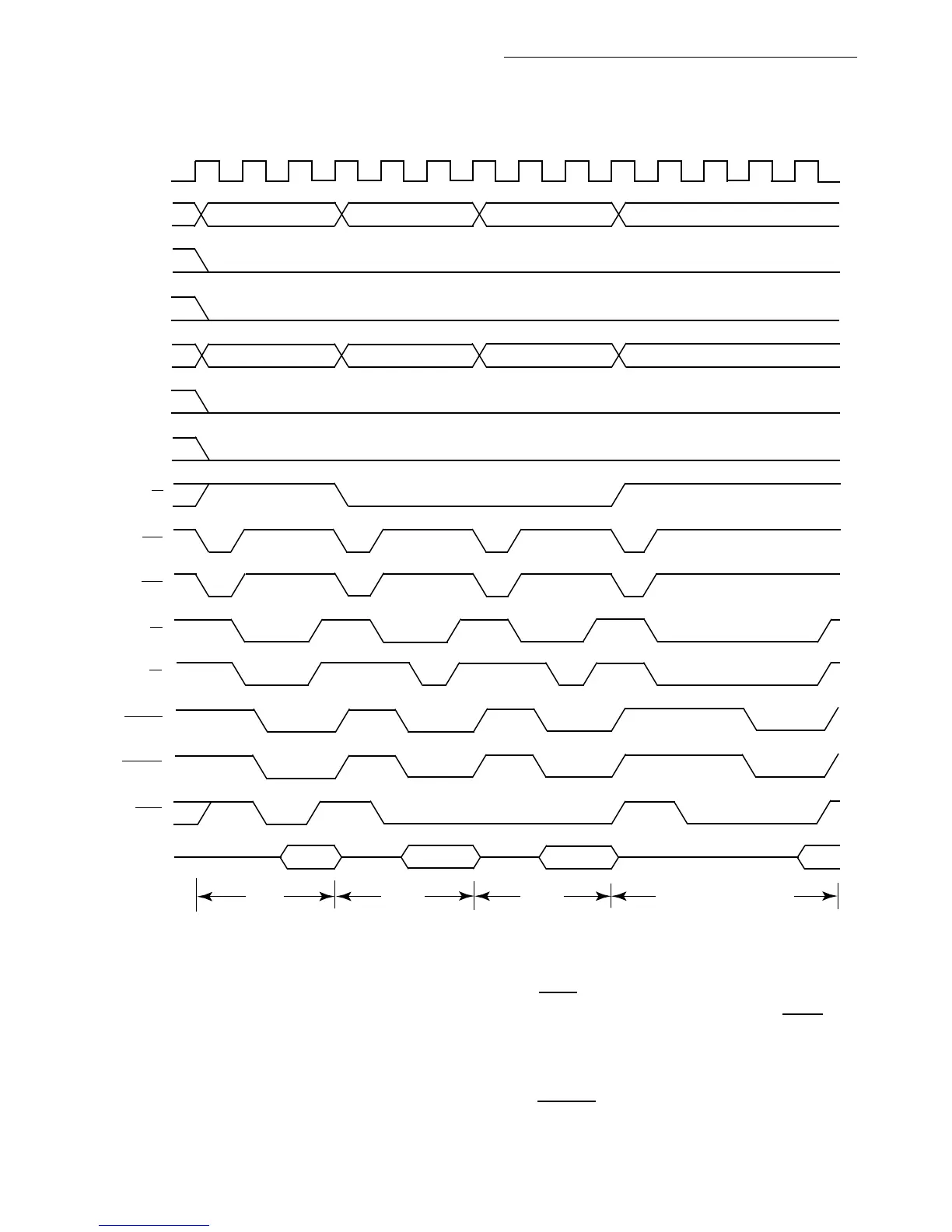

Figure 7-25. Asynchronous Read-Write-Read Cycles — 32-Bit Port

CLK

A31-A2

A1

A0

FC2-FC0

SIZ1

SIZ0

R/W

ECS

OCS

AS

DS

DSACK1

DSACK0

DBEN

D31-D0

WRITE

LONG WORD

WRITE

READ

S0 S2 S4 S0 S2 S4 S0 S2 S4 S0 S2 Sw Sw S4

READ WITH WAIT STATES

Loading...

Loading...