Bus Operation

7-58 MC68030 USER’S MANUAL MOTOROLA

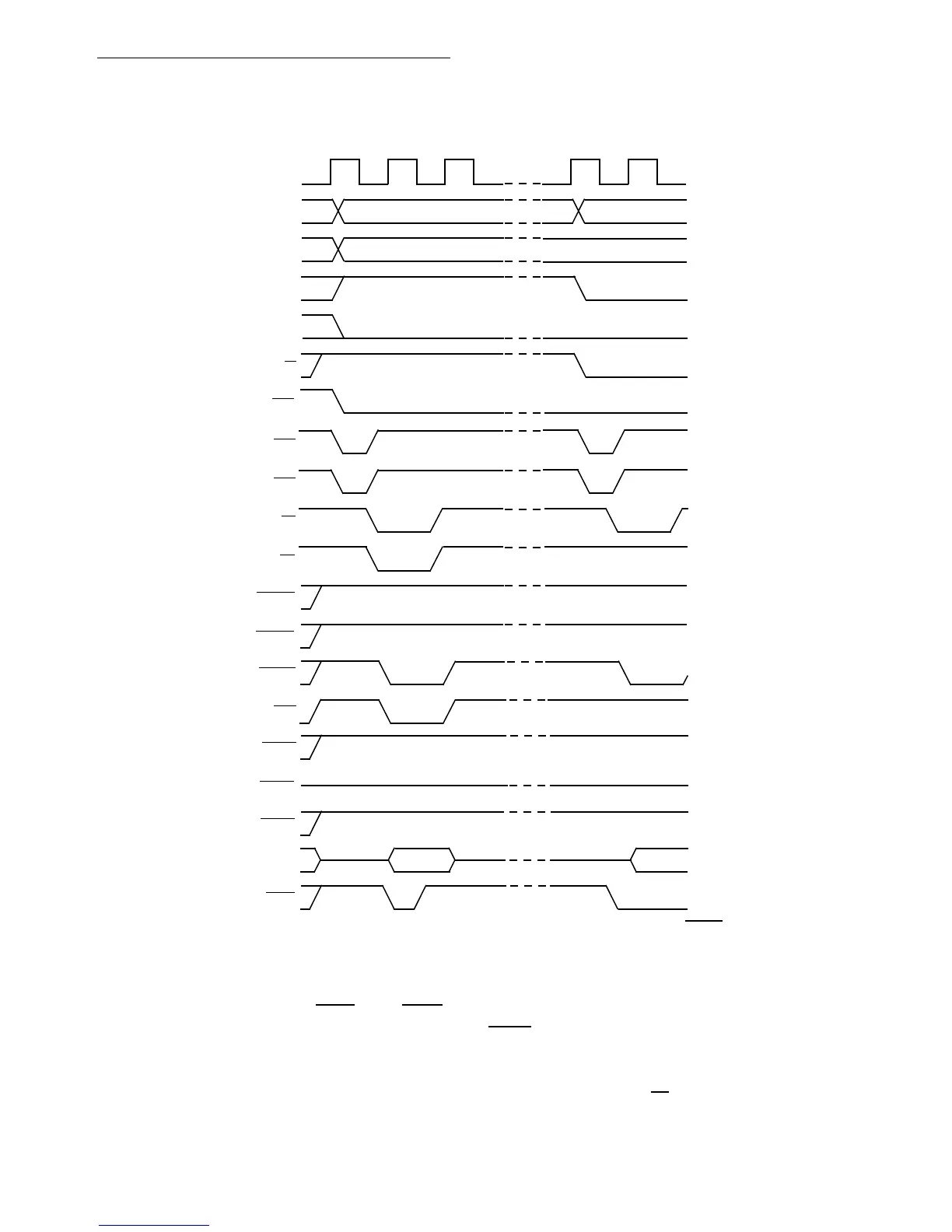

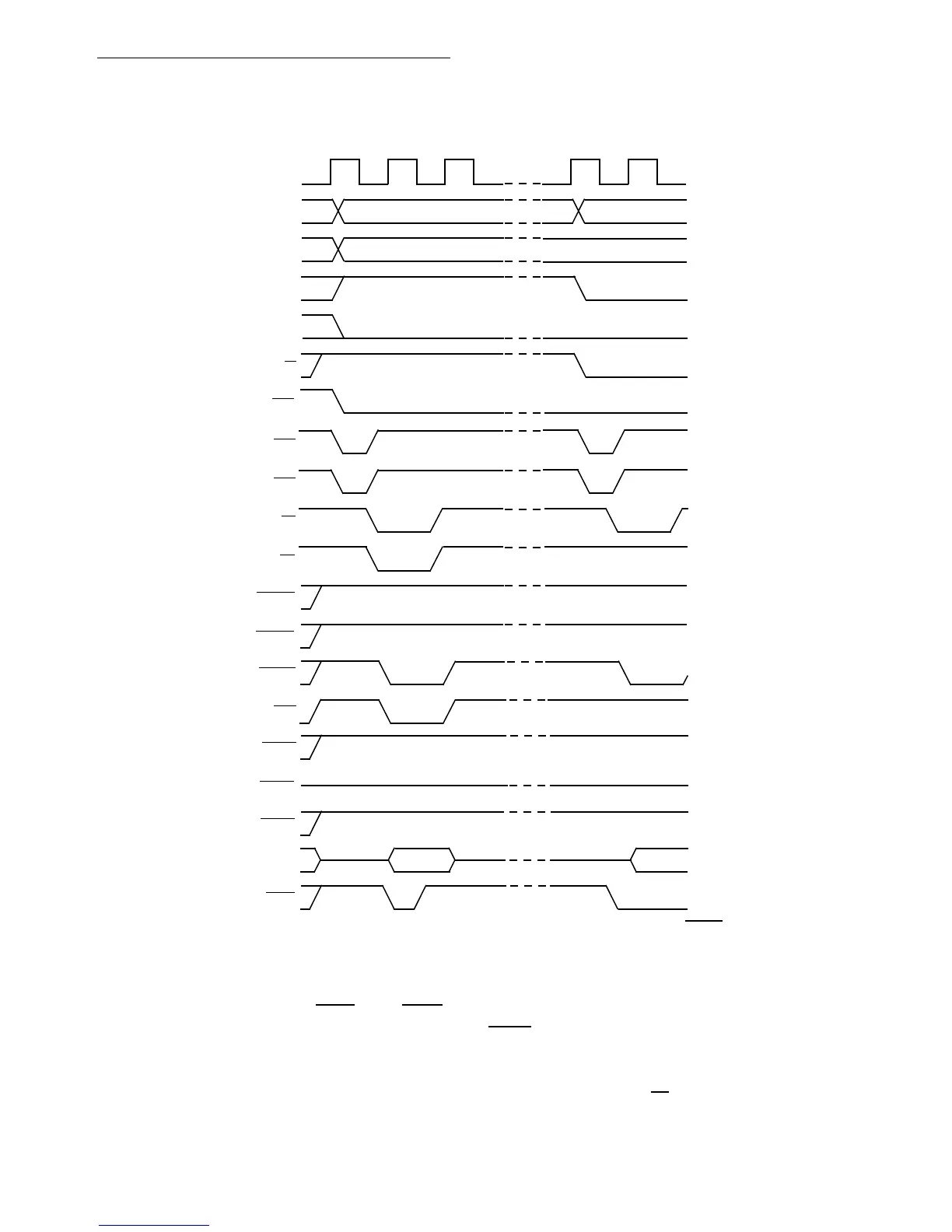

State 0

The processor asserts ECS

and OCS in S0 to indicate the beginning of an external

operand cycle. The processor also asserts RMC

in S0 to identify a read-modify-write

cycle. The processor places a valid address on A0–A31 and valid function codes on FC0–

FC2. The function codes select the address space for the operation. SIZ0–SIZ1 become

valid in S0 to indicate the operand size. The processor drives R/W

high for a read cycle

Figure 7-36. Synchronous Read-Modify-Write Cycle Timing — CIIN

Asserted

S0 S2 SiS1 S3 Si S4 S5 S6 S7

CLK

A31-A0

D31-D0

ECS

FC2-FC0

SIZ1

SIZ0

R/W

OCS

AS

DS

DSACK1

DSACK0

STERM

CIIN

CIOUT

CBREQ

CBACK

DBEN

RMC

Loading...

Loading...