Bus Operation

MOTOROLA MC68030 USER’S MANUAL 7-83

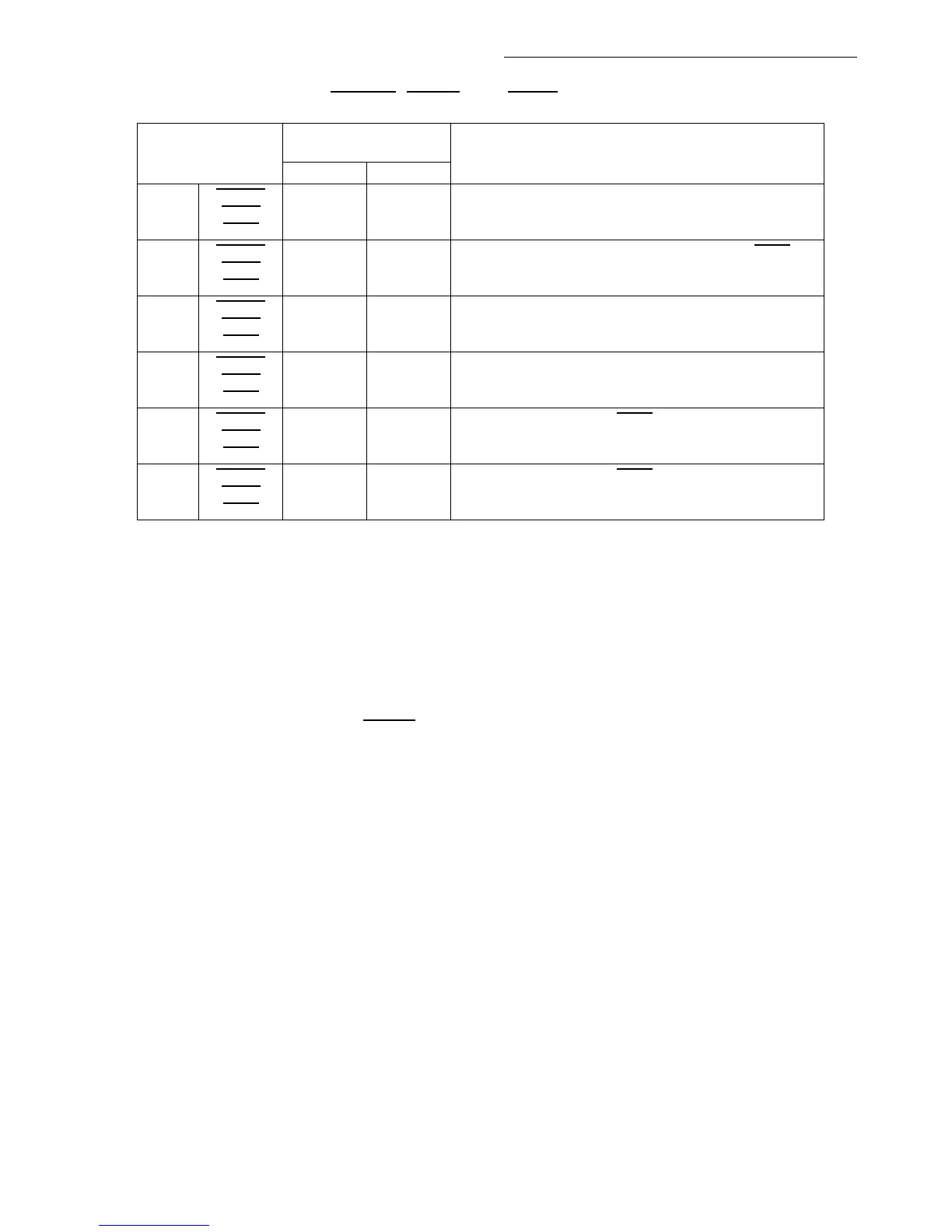

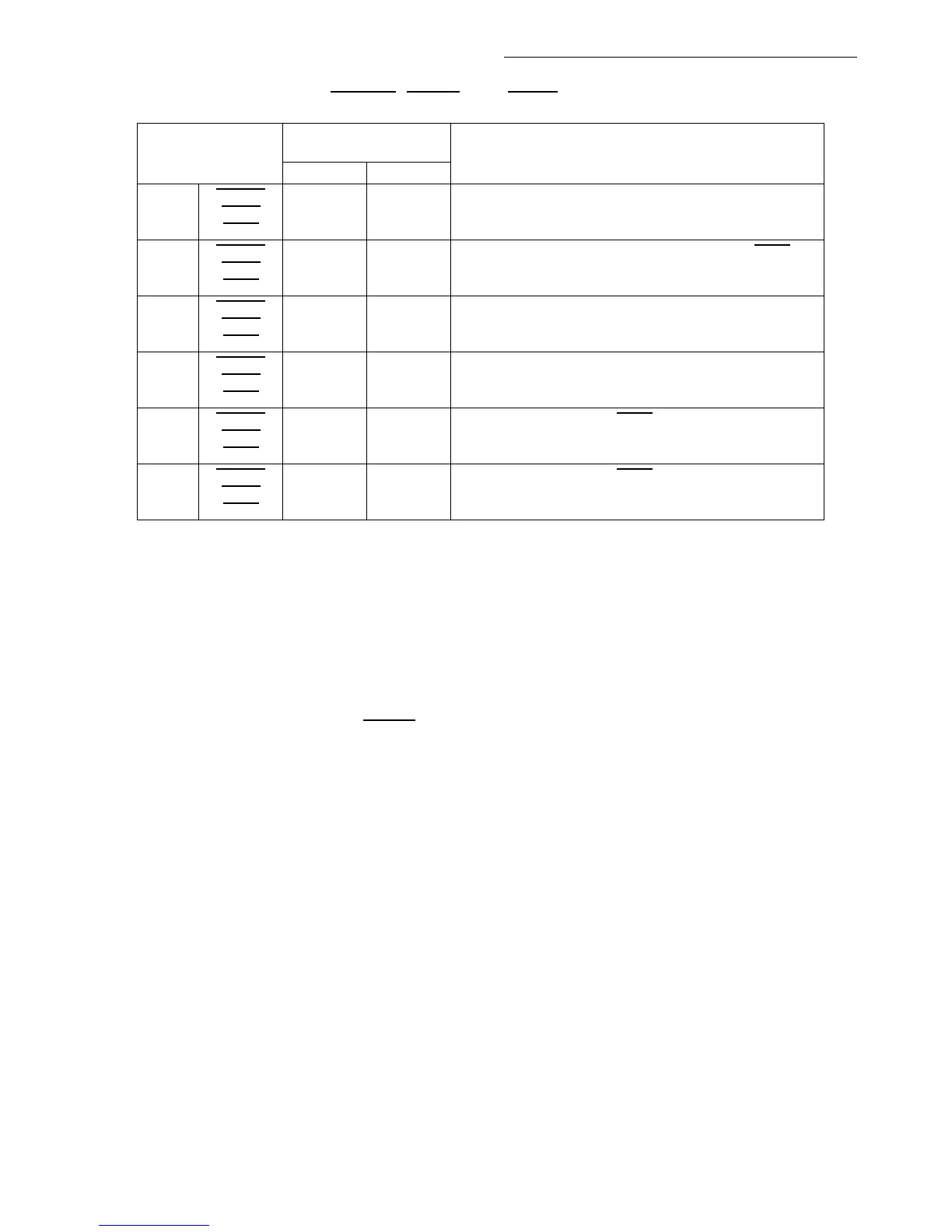

LEGEND:

N —The number of current even bus state (e.g., S2, S4, etc.)

A —Signal is asserted in this bus state

NA —Signal is not asserted in this state

X —Don't care

S —Signal was asserted in previous state and remains asserted in this state

— —State N+2 not part of bus cycle

EXAMPLE A:

A system uses a watchdog timer to terminate accesses to an unpopulated address

space. The timer asserts BERR

after timeout (case 3).

Table 7-9. STERM

, BERR, and HALT Assertion Results

Case

No.

Control

Signal

Asserted on Rising

Edge of State

Result

N N+2

1 STERM

BERR

HALT

A

NA

NA

—

—

—

Normal cycle terminate and continue.

2 STERM

BERR

HALT

NA

NA

A/S

A

NA

S

Normal cycle terminate and halt. Continue when HALT

negated.

3 STERM

BERR

HALT

NA

A/S

NA

A

S

NA

Terminate and take bus error exception, possibly

deferred.

4 STERM

BERR

HALT

A

A

N/A

—

—

—

Terminate and take bus error exception, possibly

deferred.

5 STERM

BERR

HALT

NA

A

A/S

A

S

S

Terminate and retry when HALT negated.

6 STERM

BERR

HALT

A

A

A

—

—

—

Terminate and retry when HALT negated.

Loading...

Loading...