Bus Operation

7-88 MC68030 USER’S MANUAL MOTOROLA

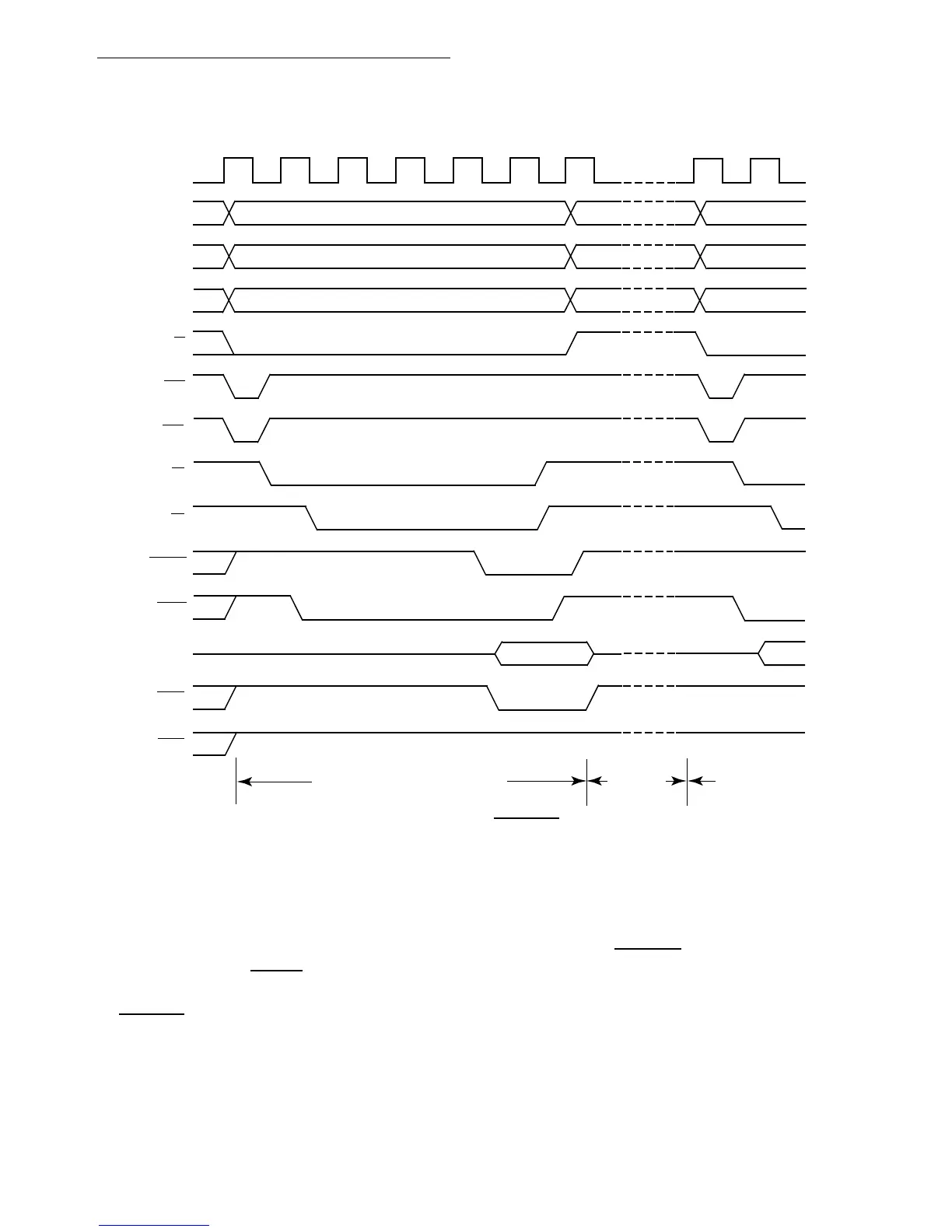

When a bus error occurs after the burst mode has been entered (that is, on the second

access or later), the processor terminates the burst operation, and the cache entry

corresponding to that cycle is marked invalid, but the processor does not take an exception

(see Figure 7-52). If the second cycle is for a portion of a misaligned operand fetch, the

processor runs another read cycle for the second portion with CBREQ

negated, as shown

in Figure 7-53. If BERR

is asserted again, the MC68030 then takes an exception. The

MC68030 supports late bus errors during a burst fill operation; the timing is the same relative

to STERM

and the clock as for a late bus error in a normal synchronous cycle.

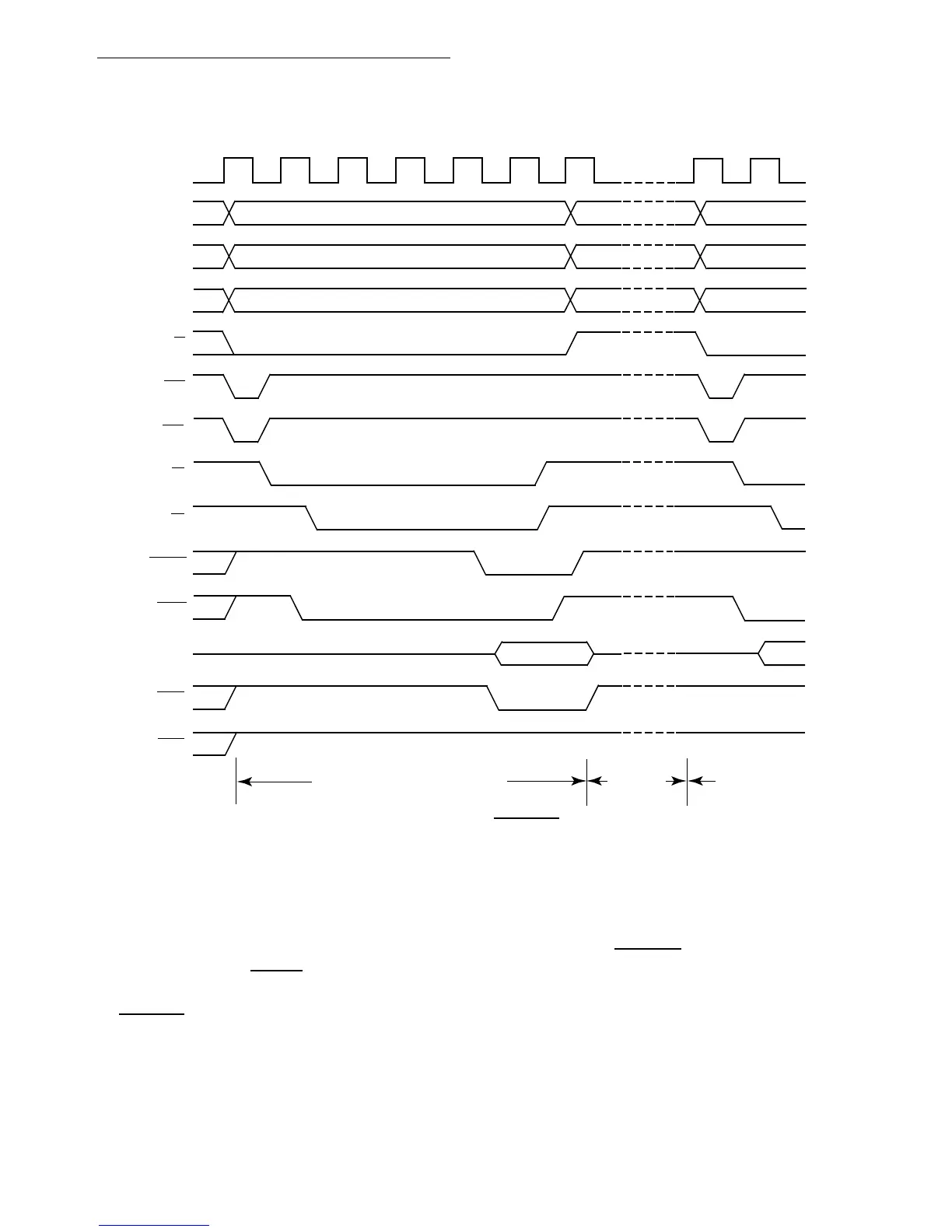

Figure 7-51. Late Bus Error with STERM — Exception Taken

AS

CLK

A31-A0

FC2-FC0

SIZ1–SIZ0

S0 S2 S3 S0 S2SwSwSw Sw

R/W

ECS

OCS

DS

STERM

DBEN

BERR

D31-D0

HALT

WRITE WITH BUS ERROR ASSERTED

INTERNAL

PROCESSING

STACK WRITE

Loading...

Loading...