Introduction

MOTOROLA

MC68030 USER’S MANUAL

1-7

The program counter (PC) contains the address of the next instruction to be executed by the

MC68030. During instruction execution and exception processing, the processor

automatically increments the contents of the PC or places a new value in the PC, as

appropriate.

The status register, SR, (see Figure 1-4) stores the processor status. It contains the

condition codes that reflect the results of a previous operation and can be used for

conditional instruction execution in a program. The condition codes are extend (X), negative

(N), zero (Z), overflow (V), and carry (C). The user byte containing the condition codes is the

only portion of the status register information available in the user privilege level, and it is

referenced as the CCR in user programs. In the supervisor privilege level, software can

access the full status register, including the interrupt priority mask (three bits) as well as

additional control bits. These bits indicate whether the processor is in:

1. One of two trace modes (T1, T0)

2. Supervisor or user privilege level (S)

3. Master or interrupt mode (M)

The vector base register (VBR) contains the base address of the exception vector table in

memory. The displacement of an exception vector is added to the value in this register to

access the vector table.

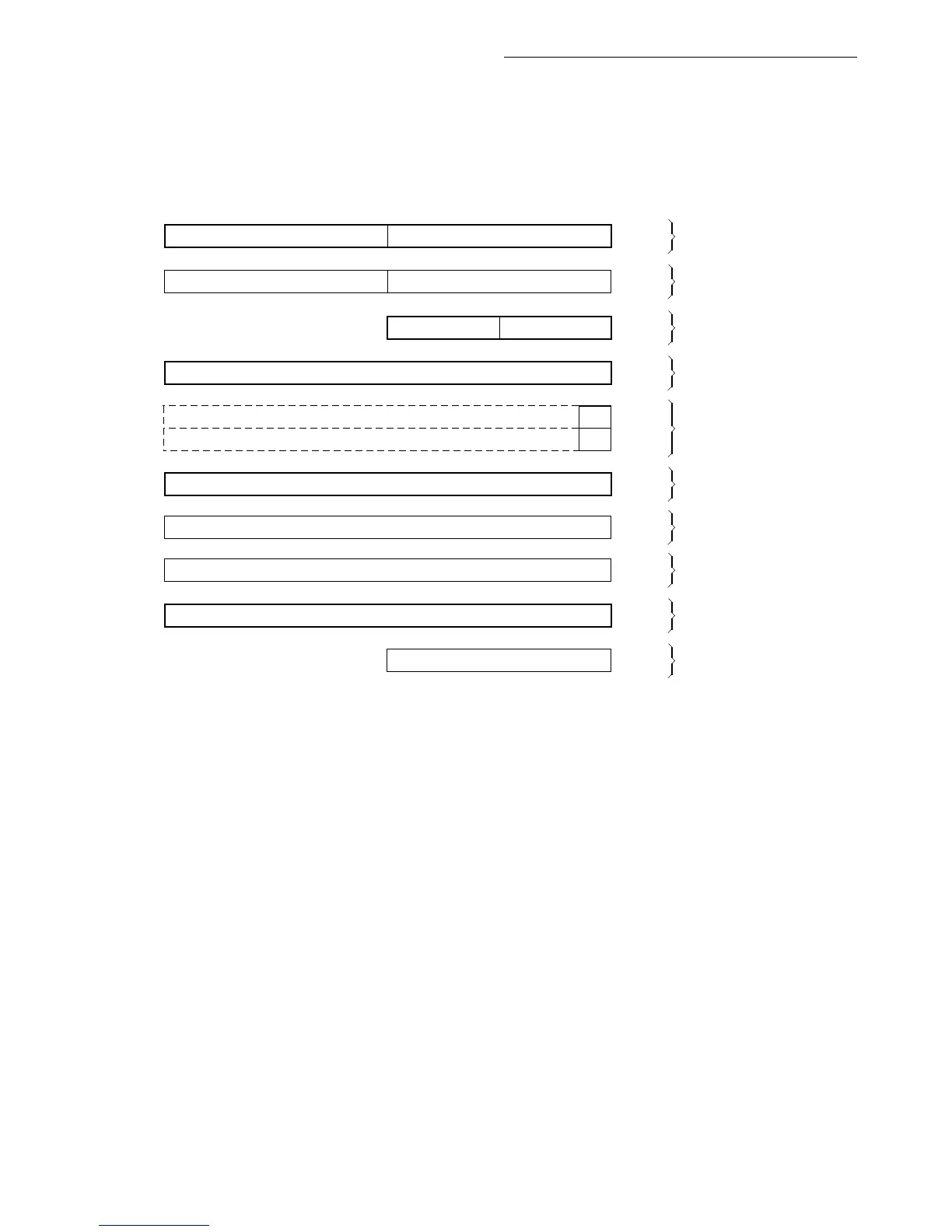

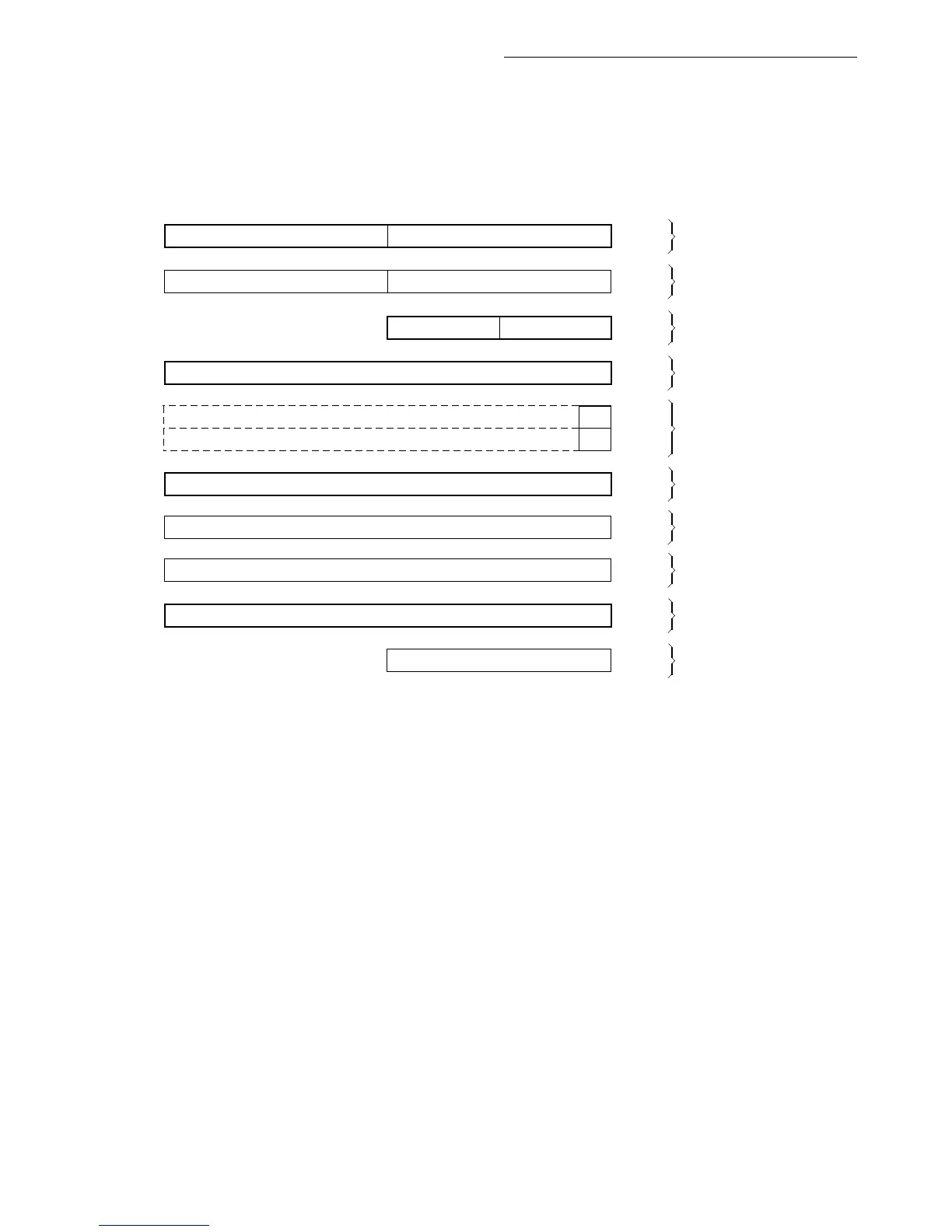

Figure 1-3. Supervisor Programming Model Supplement

31

16 15

0

31

16 15

0

15

87 0

(CCR) SR

A7" (MSP)

A7' (ISP)

31

0

VBR

SFC

DFC

CACR

CAAR

INTERRUPT

STACK POINTER

MASTER STACK

POINTER

STATUS REGISTER

VECTOR BASE

REGISTER

ALTERNATE FUNCTION

CODE REGISTERS

CACHE CONTROL

REGISTER

CACHE ADDRESS

REGISTER

0

0

0

31

31

31

AC0

ACCESS

CONTROL

REGISTER 0

0

31

AC1

ACCESS

CONTROL

REGISTER 1

0

31

ACUSR

ACU STATUS

REGISTER

0

15

Loading...

Loading...