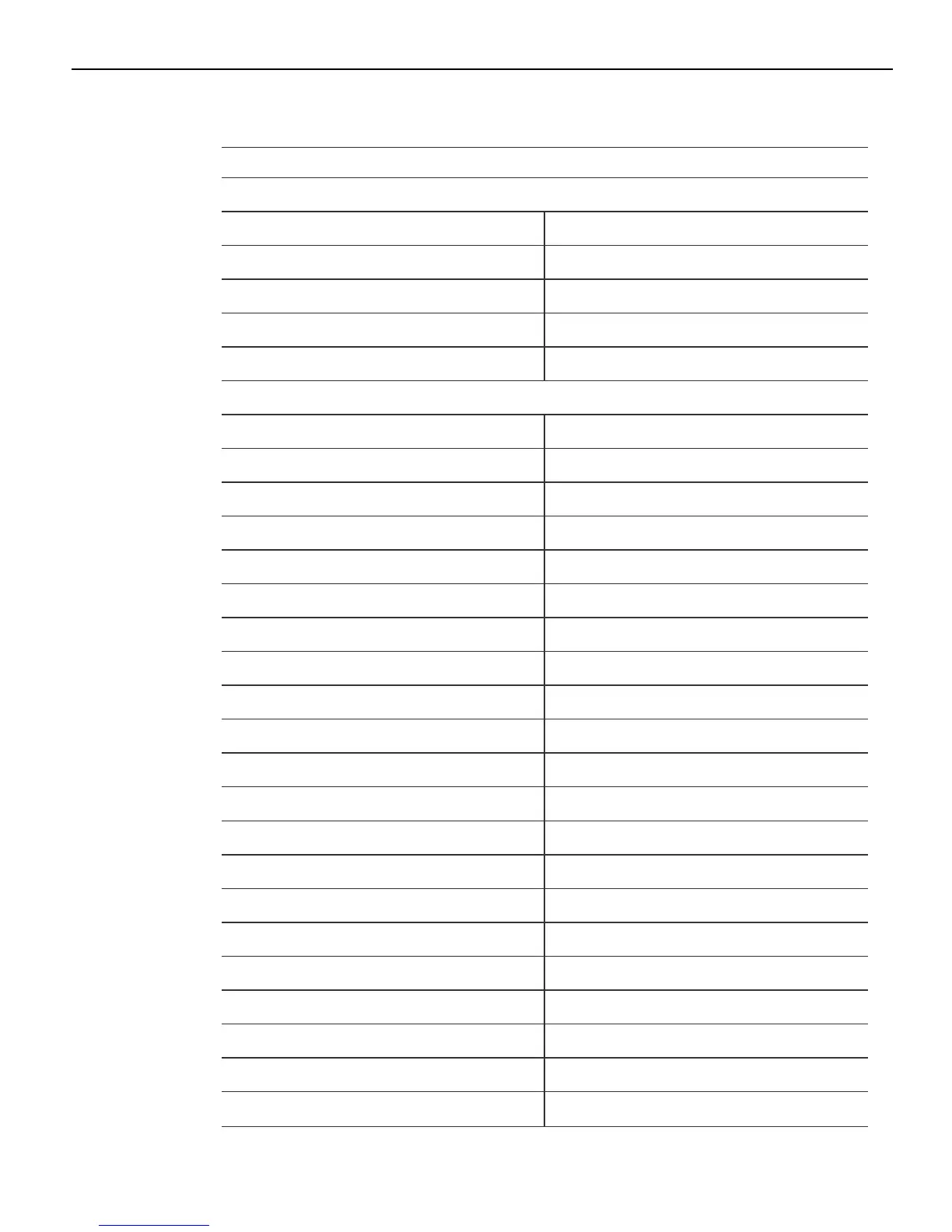

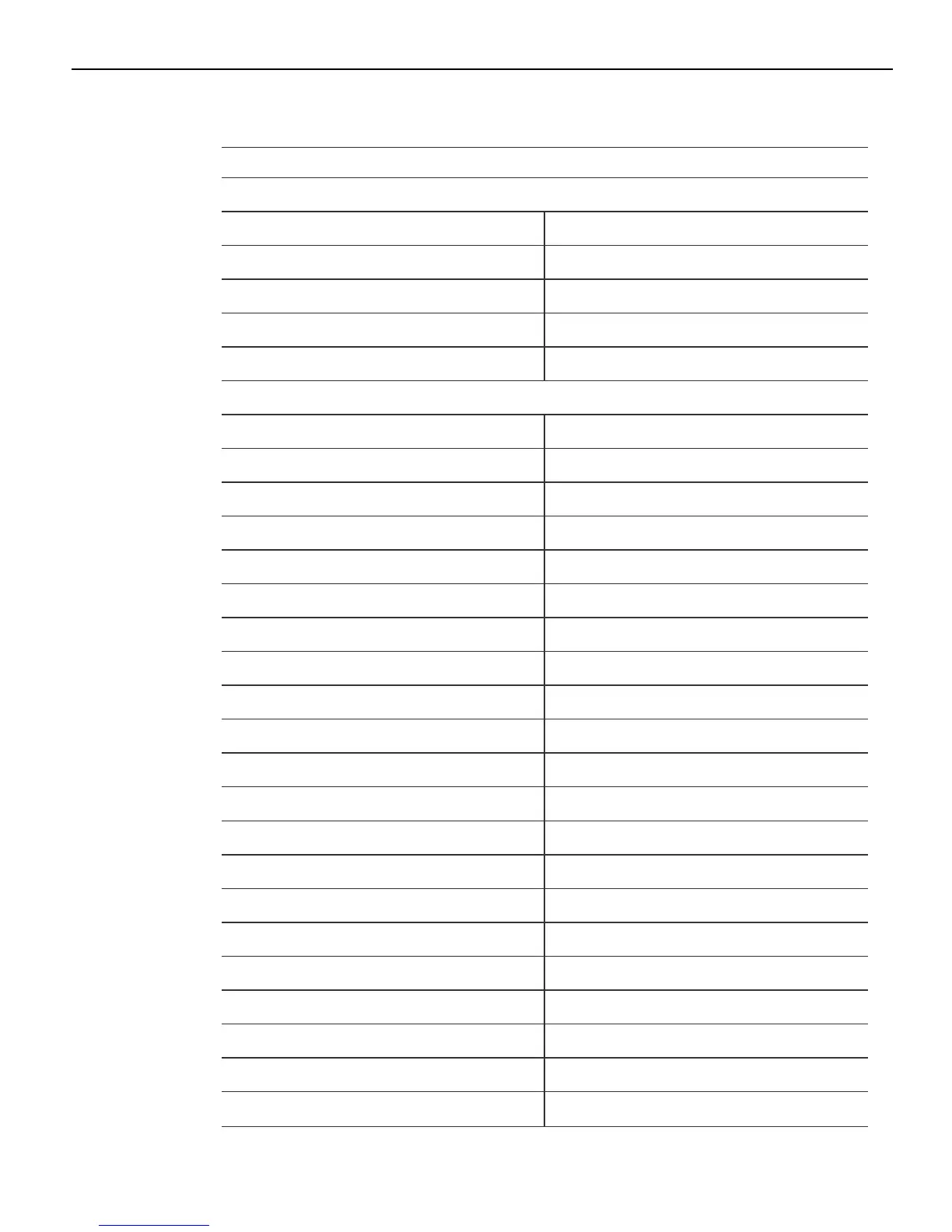

Initial Terminal Imaging 5-109

Chipset

► PCH-IO Configuration

. ► PCI Express Configuration

. PCI Express Clock Gating [Enabled]

. DMI Link ASPM Control [Enabled]

. DMI Link Extended Synch Control [Disabled]

. PCIE Root Port Function Swapping [Enabled]

. Subtractive Decode [Disabled]

. ► PCI Express Root Port 1,2,4,5,6,7,8

. PCI Express Root Port 1,2,4,5,6,7,8 [Enabled]

. ASPM Support [Auto]

. . URR [Disabled]

. . FER [Disabled]

. . NFER [Disabled]

. . CER [Disabled]

. . CTO [Disabled]

. . SEFE [Disabled]

. . SENFE [Disabled]

. . SECE [Disabled]

. . PME SCI [Enabled]

. . Hot Plug [Disabled]

. PCIe Speed [Auto]

. Detect Non-Compliance Device [Disabled]

. Extra Bus Reserved 0

. Resreved Memory 10

. Reserved I/O 4

. PCIE LTR [Enabled]

. PCIE LTR Lock [Enabled]

. Snoop Latency Override [Auto]

. Non Snoop Latency Override [Auto]

Loading...

Loading...