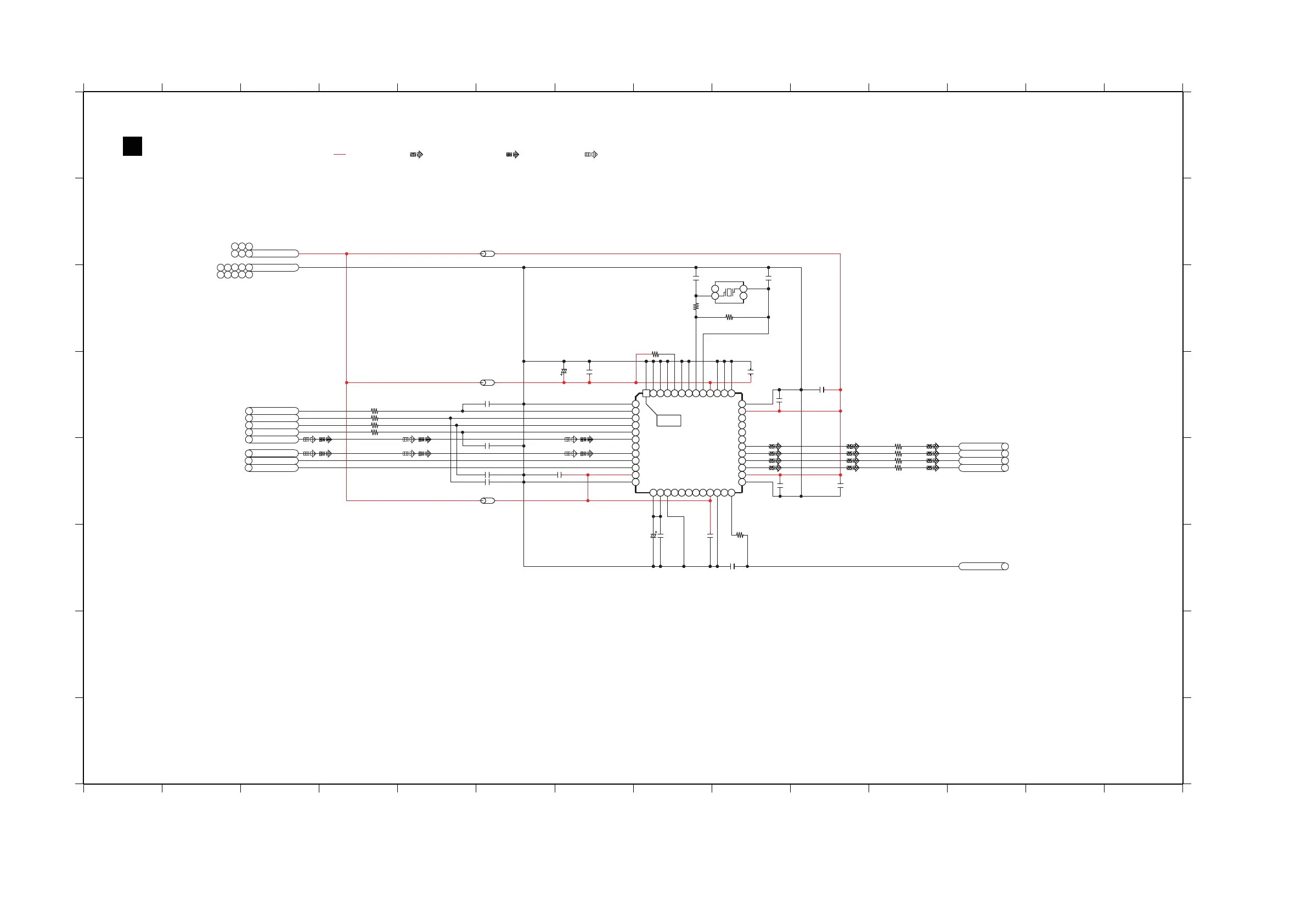

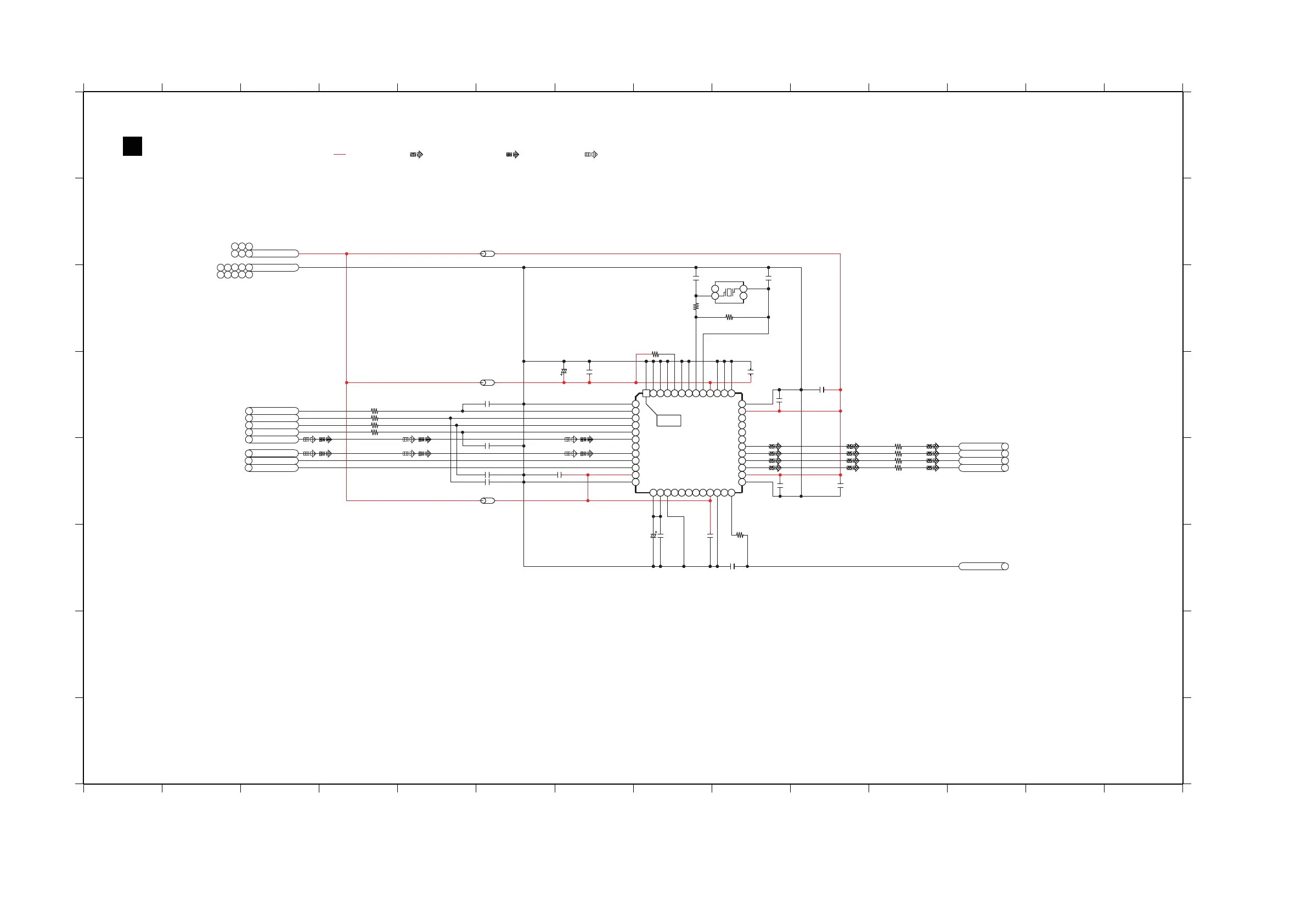

12.7. Main (DSP) Circuit

A

1

2 3 4 5 6 7 8 9 10 11 12 13 14

1 2 3 4 5 6 7 8 9 10 11 12 13 14

C

D

B

E

G

H

F

A

C

D

B

E

G

H

F

SC-UA3E/GN/PR/PU MAIN (DSP) CIRCUIT

A

MAIN (DSP) CIRCUIT

: +B SIGNAL LINE

: CD SIGNAL LINE

: OUTPUT SIGNAL LINE

: MIC/AUX/TUNER SIGNAL LINE

SCHEMATIC DIAGRAM - 6

MA: MAIN (MAIN): SCHEMATIC DIAGRAM - 1 ~ 2

BT: MAIN (BLUETOOTH): SCHEMATIC DIAGRAM - 3

CO: MAIN (CONNECTOR): SCHEMATIC DIAGRAM - 3

FL: MAIN (FAN LED): SCHEMATIC DIAGRAM - 3

FE: MAIN (FE): SCHEMATIC DIAGRAM - 4

DA: MAIN (DAMP): SCHEMATIC DIAGRAM - 5

OP: MAIN (OPT_SRC): SCHEMATIC DIAGRAM - 7

TU: MAIN (TUNER AUX): SCHEMATIC DIAGRAM - 8

US: MAIN (USB): SCHEMATIC DIAGRAM - 8

VR: MAIN (VOLTAGE REGULATOR): SCHEMATIC DIAGRAM - 9

DSP_SDO0

LB6500

J0JYC0000656

J0JYC0000656

LB6501

C6550

1000P

DSP_SDO1

R6521 47

R6520 47

R6550 220

R6551 220

C6551 1000P

C6553 47P

C6552 47P

PWM_M_2

PWM_P_2

R6501

1.5K

12P

C6560

1M

R6502

2

3

1

4

H0J245500110

X6500

C6561

12P

C6529

1

R6504

10K

C6530

6.3V47 10

C6528

C6526

0.01

10

C6525

J0JYC0000656

LB6502

PWM_M_1

100R6511

C6592

0.1

C6591

1

100

R6559

C6521

0.47

DAMP_VALID

10

C6524C6523

0.01

C6500

6.3V47

100R6513

100R6514

PWM_P_1

100R6512

C6527 1

4

5

T1 4546 4448 47

2

1

3

32

34

36

35

33

42 404143 3739 38

8

15

16 17

13 14

9

6

7

27

25

22 232019

21 24

26

18

30

31

28

29

THERMAL

PAD

11

12

10

IC6500

VUEALLPT090

DSP

DSP_RESET

DSP_SCL

DSP_MUTE

DSP_SDA

DGND

PW_3R3V

DSP_WCK

G_DSP_BCK

BCK

PWM1A

PWM1B

LRCK

[11]DVDD1

[12]DVSSCORE

LDOPOFF

ERRIN

SDOUT1

SDOUT2

REG15

DVDDCORE

BCKO

LRCK

DVSS2

DVDD2

CLKO

VALID

DVDD_PWM1[26]

DVSS_PWM1[25]

SDA

SCL

SMUTE

PWM3A

PWM4B

[1]DVSS1

[2]RST_N

DVSS_PWM2[36]

DVDD_PWM1[35]

PWM4A[34]

CLK110M

ANATEST

BSSEL

ADDR

XI

XO

AVSS

AVDD

XINSEL

TST

DIVSEL

DVSS_OSC

PWM2B

SDIN1

PWM3B

PWM2A

SDIN3

SDIN2

DA

DA

DA

DA

DA

MI

MI

MI

MI

MI

MI

MI

MI

MI

TU

OP

US

VR

DA

BT

CO FE

FE

OP VR

DA CO TU

FL

Loading...

Loading...