Circuit Descriptions, Abbreviation List, and IC Data Sheets

EN 82 LC7.2E LB9.

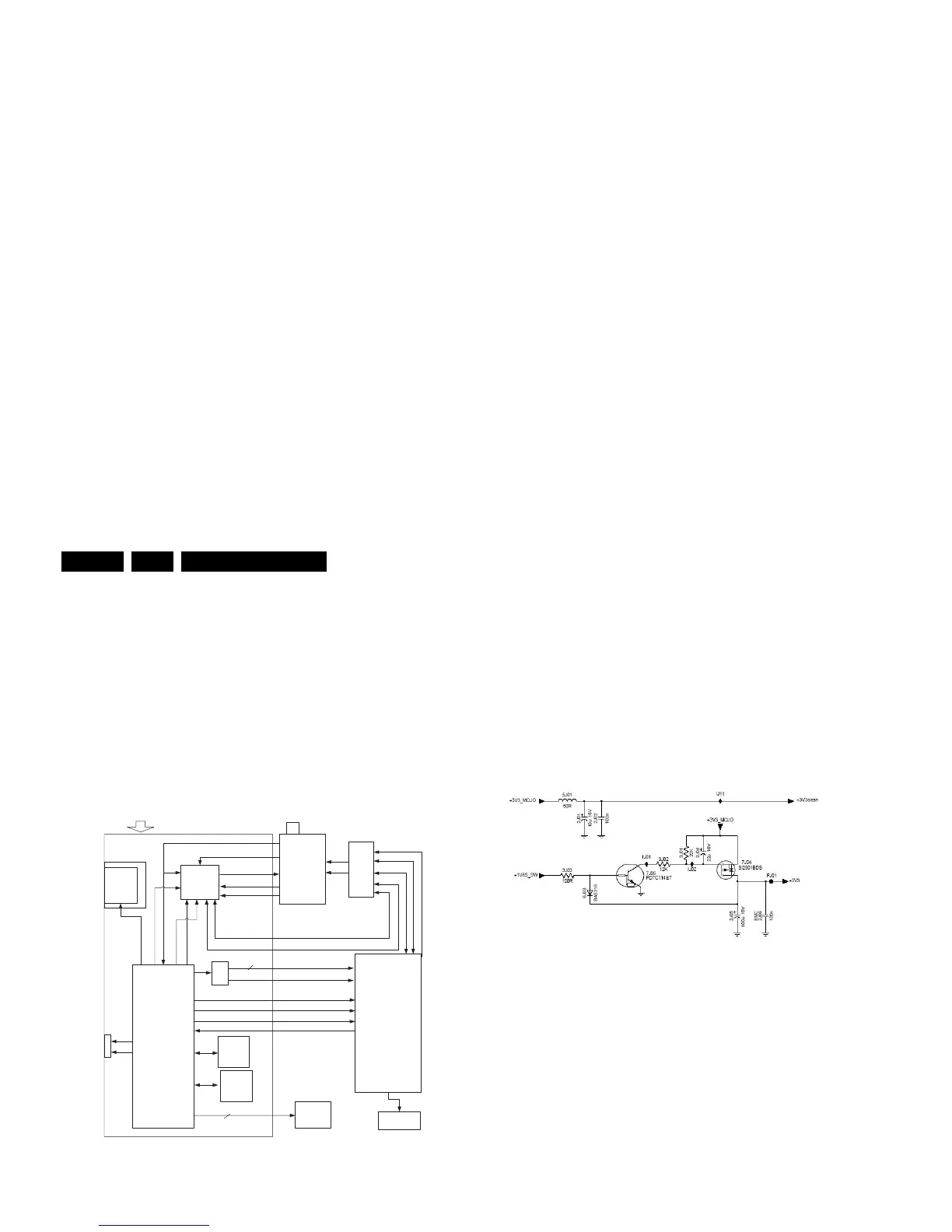

9.5 DVB-T Signal Processing

The DVB-T cell on the SSB is built around the “MOJO” MPEG

decoder PNX8314HS (item 7G00) and receives the signal from

the COFDM Channel Decoder TDA10046 (item 7F01). The

(hybrid) tuner TD1316AF (item 1101) supports digital (DVB-T)

reception and transports the signal via the VIM_IBO and

VIP_IBO lines. The digital data stream exits the DVB-T cell

when it is fed to the Trident SVP CX32 Video Processor (item

7202). A Common Interface (CI) slot allows reception of

encoded signals when used with a Conditional Access Module

(CAM) in combination with a smart card. See figure “Block

diagram DVB-T reception” for details.

Figure 9-5 Block diagram DVB-T reception

9.5.1 Common Interface (CI)

Introduction

The digital sets of this chassis are provided with a special slot

called Common Interface (CI). Together with a Conditional

Access Module (CAM) and a smart card, it is possible to

receive scrambled TV programs. This means that it is not

necessary to have a separate Set Top Box to receive digital

cable SDTV and HDTV programs (however this still is

possible).

The removable smart card, distributed by cable companies,

allows you to tune digital and high definition scrambled or

encrypted cable channels through the cable antenna. The

smart card is also required to receive premium digital TV

channels and services (where available) through the cable. A

smart card functionality includes conditional access and copy

protection.

Implementation

1. The receiver receives the digital data stream.

2. The data flows into the Conditional Access Module, which

contains the content provider's unscrambling algorithms.

3. This module verifies the existence of a smart card that

contains the subscriber's authorization code.

4. If the authorization code is accepted, the CAM

unscrambles the data and returns the data to the receiver

(if the code is not accepted, the data remains scrambled,

restricting access).

5. The receiver then decodes the data and outputs it for

viewing.

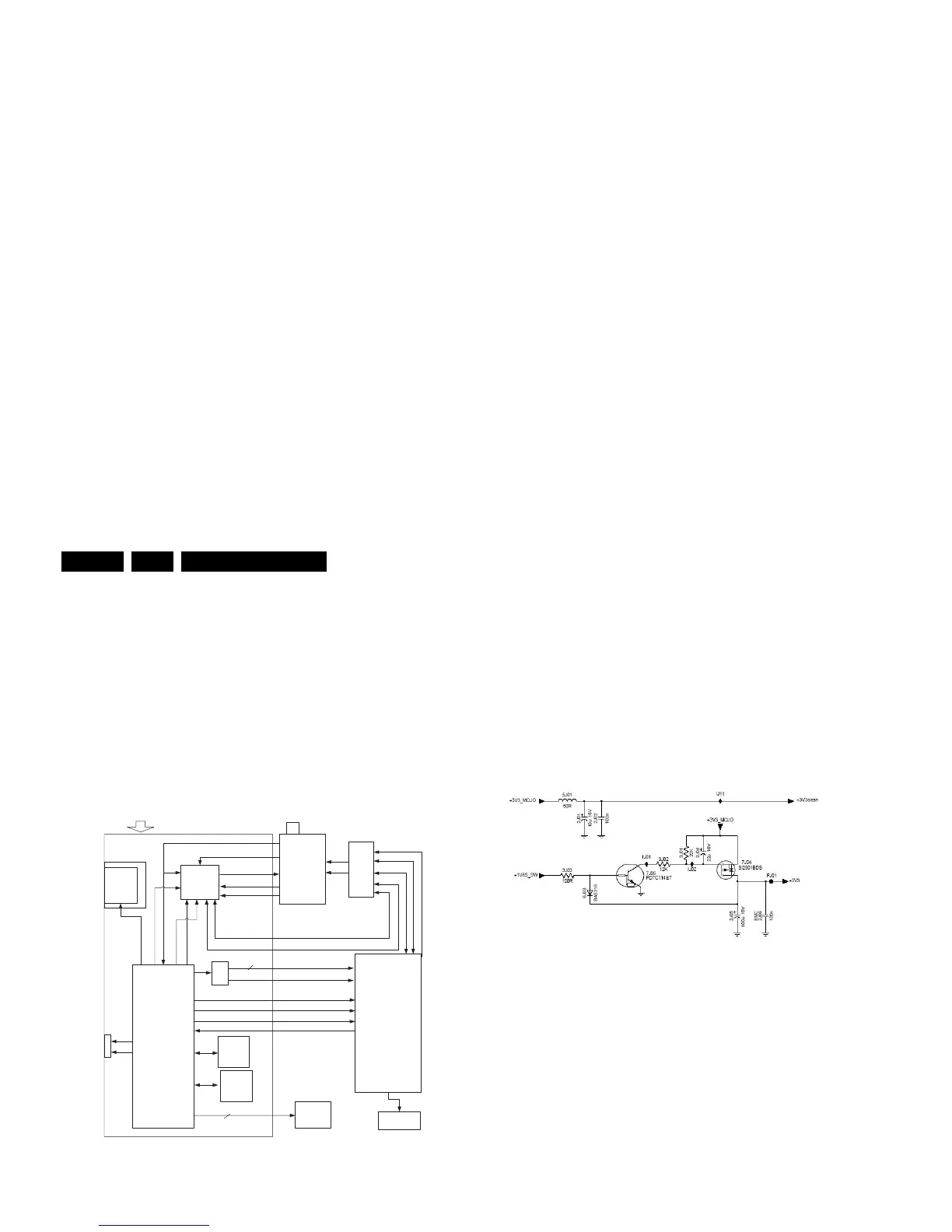

9.5.2 Supply

The internal voltages that are used are:

• 5 V (+5V_SW)

• 3.3 V (+3V3_MOJO)

• 1.2 V (+1V2_MOJO)

• 1.8 V (+1V8S_SW).

During start-up, it is important that the +1V8S_SW line comes

up earlier than the +3V3_MOJO line. In order to implement this,

a delay circuit is added which is shown in figure “Delay

circuitry”.

Figure 9-6 Delay circuitry

Item 7J05 switches the MOSFET “on” and “off” (item 7J04).

The diode (item 6J03) performs a short-circuit protection for the

+3V3 output stage.

9.6 Video Processing

The video processing is completely handled by the Trident SVP

CX32 video processor which features:

• CVBS-input for analogue signals.

• RGB-input for digital (DVB-T) signals.

• Motion and “edge-adaptive” de-interlacing.

• Integrated ADC.

• Built-in 8-bit LVDS transmitter.

• Colour stretch.

• Skin colour enhancement.

• 3D Digital Comb Video Decoder.

• Interlaced and Progressive Scan refresh.

• TeleText decoding.

• OSD and VBI/Closed Caption.

9.6.1 Video Application

Figure 9-7 Block diagram video processing

1V2_MOJO

1V8S_SW

3V3_MOJO

LC07 EU DVB Cell

TRIDENT/uP

MOJO

LPF

IBO_R,G,B

IBO_CVBS

TDA10046

Channel

Decoder

HYBRID

TUNER

MUX

TDA_SDA

TDA_SCL

I

2

C_SCL

I

2

C_SDA

DVB_SW

4MHz CLK

SCL

SDA

VIP_IBO

VIM_IBO

IF_AGC_IBO

RF_AGC_IBO

Multi

Sound

Processor

I

2

S (SD, WS, SCLK)

CI SLOT

(STV0700)

UART

TXD0

RXD0

IBO_I

2

C_SD

IBO_I

2

C_SCL

IBO_IRQ

RESET_n

FLASH

SDRAM

I

2

C_LOCAL SDA

I

2

C_LOCAL SCL

RESET_FE_n

RESET_STV

SCART 2

G_16860_057.eps

310107

G_16860_058.eps

310107

IB O _ R _IN

Trident

Video Processor

SVP CX32

(DVB-T

demodu la to r

DigDŽ Front End

a nd decoder)

CVBS

S CART1

S C1_R_IN

S C1_CVBS _IN

S C1_FBL_IN

HD_Y_IN

S CART2

S IDE AV

FRONT_Y_CVBS _IN_T

S C2_Y_CVBS _IN

EXT4

HDMI

Decoder

HDMI1

HDMI2

HDMI_Y(0:7)

HDMI_Cb (0 :7)

HDMI_Cr(0:7)

On b o ard E XT3

CVBS

SCART 1 Mon. out

PR_R2

PB_B2

Y_G2

S C1_G_IN

S C1_B_IN

PB_B3

FB1

IB O _ G _IN

IB O _ B_ IN

IB O _C VB S _IN

PC_R

PC_G

PC_B

F S 1

HD_PB_IN

HD_PR_IN

Y_G1

PB_B1

PR_R1

S C2_C_IN

FRONT_C_IN_T

Y_G3

C

PR_R3

F S 2

CVBS _OUT1

CVBS _OUT2

Ana lo gu e

Front End

CVBS _RF

CVBS 1

G_16860_060.eps

150307

SCART 2 Mon. out

Loading...

Loading...