Circuit Descriptions, Abbreviation List, and IC Data Sheets

EN 143Q528.2E LB 9.

9.5.4 Diagram B03C, TDA10023HT (IC7TA4)

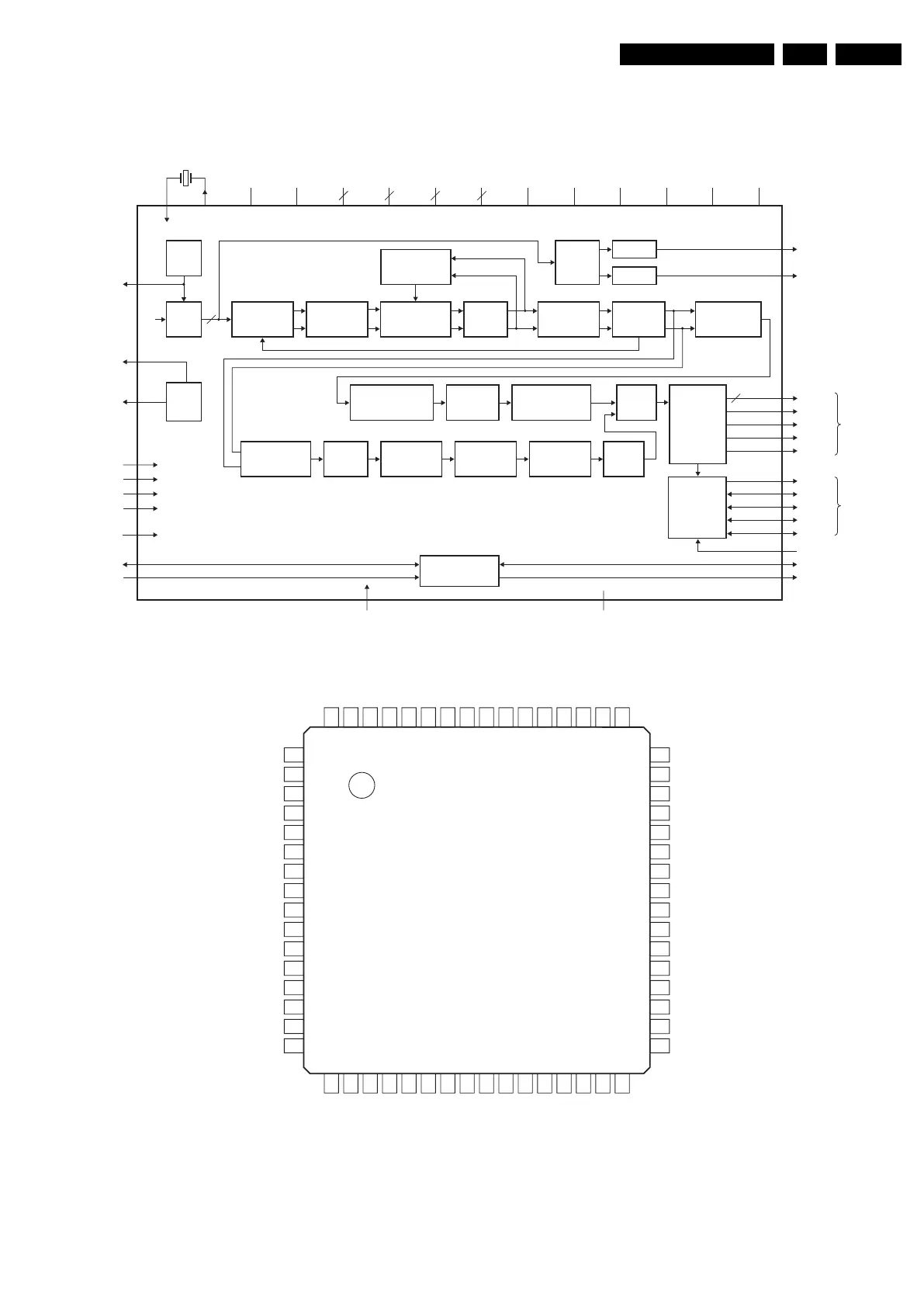

Figure 9-10 Internal block diagram and pin configuration

001aac555

CLOCK

RECOVERY

I

2

C-BUS

INTERFACE

GPIO

AGC

PWM

PWM

TIMING

INTERPOLATOR

RS

DECODER

TRELLIS

DEMODULATOR

FRAME

SYNC

DE-

RANDOMIZER

DE-

INTERLEAVER

REED

SOLOMON

DECODER

MPEG2

TS

CKSUM

JQAM

FILTER

OUTPUT

INTERFACE

JTAG

DE-SCRAMBLER

DE-INTERLEAVER

DECIMATION

FILTERS

BASEBAND

CONVERSION

ADC

PLL

EQUALIZER

HALF

NYQUIST

CARRIER

RECOVERY

DECISION

DIFFERENTIAL

DECODER

10

8

IF

TDA10023HT

23

0695551694

0

514

,

4

2

,74

1

5

9

11

17

13, 51, 52, 53, 54, 56, 62, 63, 64

18

19

SACLK

AGCTUN

AGCIF

SCL

SDA SDAT

DEN

OCLK

programmable

interface

serial

interface

PSYNC

UNCOR

DO[7:0]

37 to 40,

45 to 48

36

35

34

33

20

21

22

23

26

27

28

32

29

6

16

58

57

10

SCLT

ENSERI

TCK

TDI

TRST

TMS

TDO

CTRL

GPIO

3

V

DDD3

8, 25, 42

3

V

SSD3

14, 30, 43

3

V

DDD2

15, 31, 44

3

V

SSD2

V

DDD4

V

DDD1

V

SSD1

V

SSA1

V

DDA1

V

DDA3

V

SSA3

TEST

IICDIV

CLRB

VIP

VIM

n.c.

V

DDA2

XIN XOUT

12

SADDR

Block Diagram

Pin Configuration

H_17650_072.eps

150108

TDA10023HT

V

DDA1

DO[0]

XIN DO[1]

XOUT DO[2]

V

SSA1

DO[3]

SACLK V

SSD2

TEST V

DDD2

V

DDD3

V

SSD3

V

SSD3

V

DDD3

AGCTUN DO[4]

IICDIV DO[5]

AGCIF DO[6]

SADDR DO[7]

n.c. DEN

V

DDD2

OCLK

V

SSD2

PSYNC

CLRB UNCOR

SCL

n.c.

SDA n.c.

SDAT n.c.

SCLT

V

DDA2

ENSERI V

DDD4

TCK

V

SSA3

TDI VIP

V

DDD3

VIM

V

SSD3

n.c.

TRST V

DDA3

TMS n.c.

TDO n.c.

GPIO n.c.

V

DDD2

n.c.

V

SSD2

V

DDD1

CTRL V

SSD1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

Loading...

Loading...