114 Rabbit 2000/3000 Microprocessor

Description

Loads the Interrupt Priority register (IP) with the data whose address is in SP. Then loads the low order byte

of PC with the data whose address is 1 higher than the data in SP and loads the high order byte of PC with the

data whose address is two higher than the data in SP. The data in SP is then incremented three times. This is a

privileged instruction.

RETI

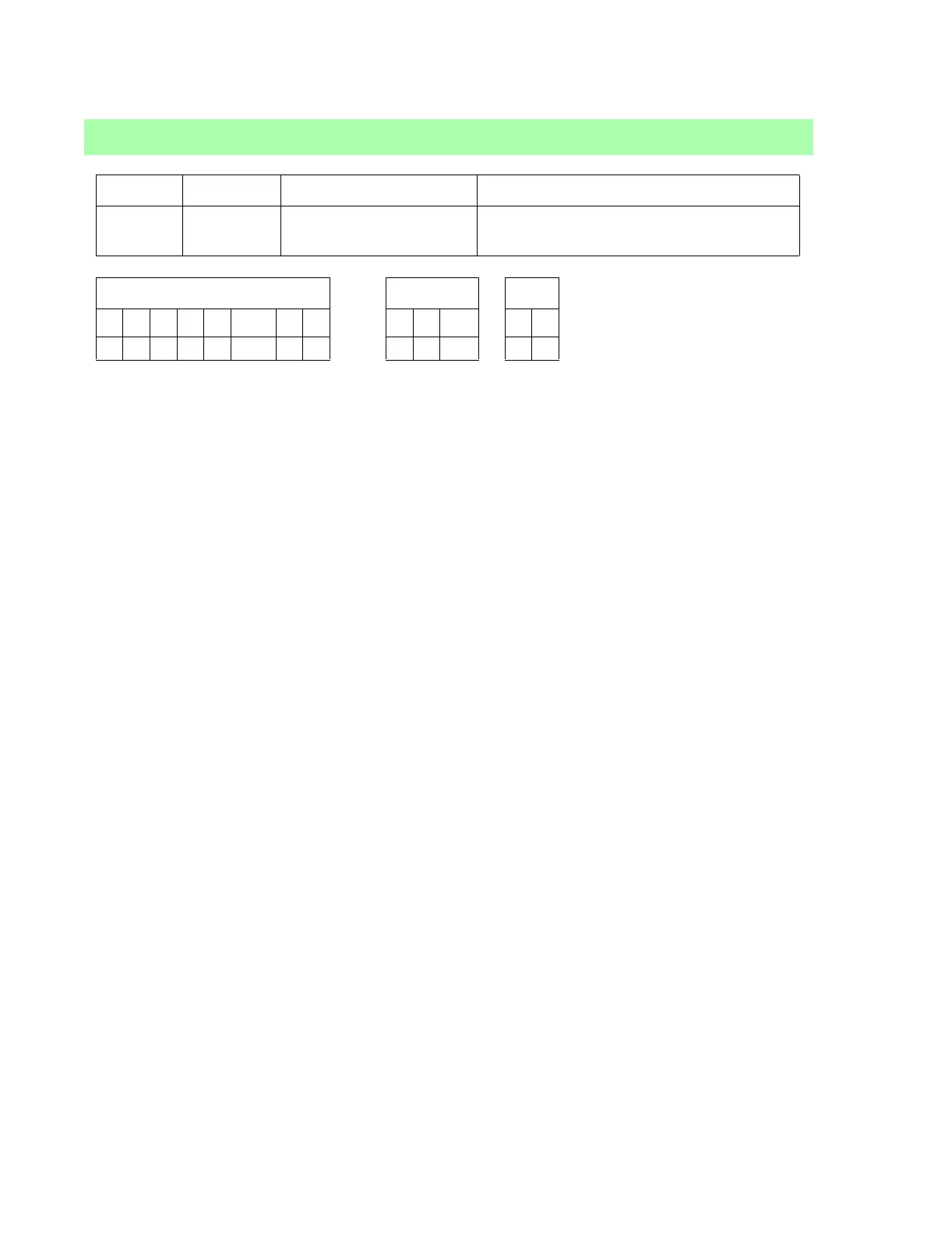

Opcode Instruction Clocks Operation

ED 4D RETI 12 (2,2,1,2,2,2,1) IP = (SP); PC

(low)

= (SP+1);

PC

(high)

= (SP + 2); SP = SP + 3

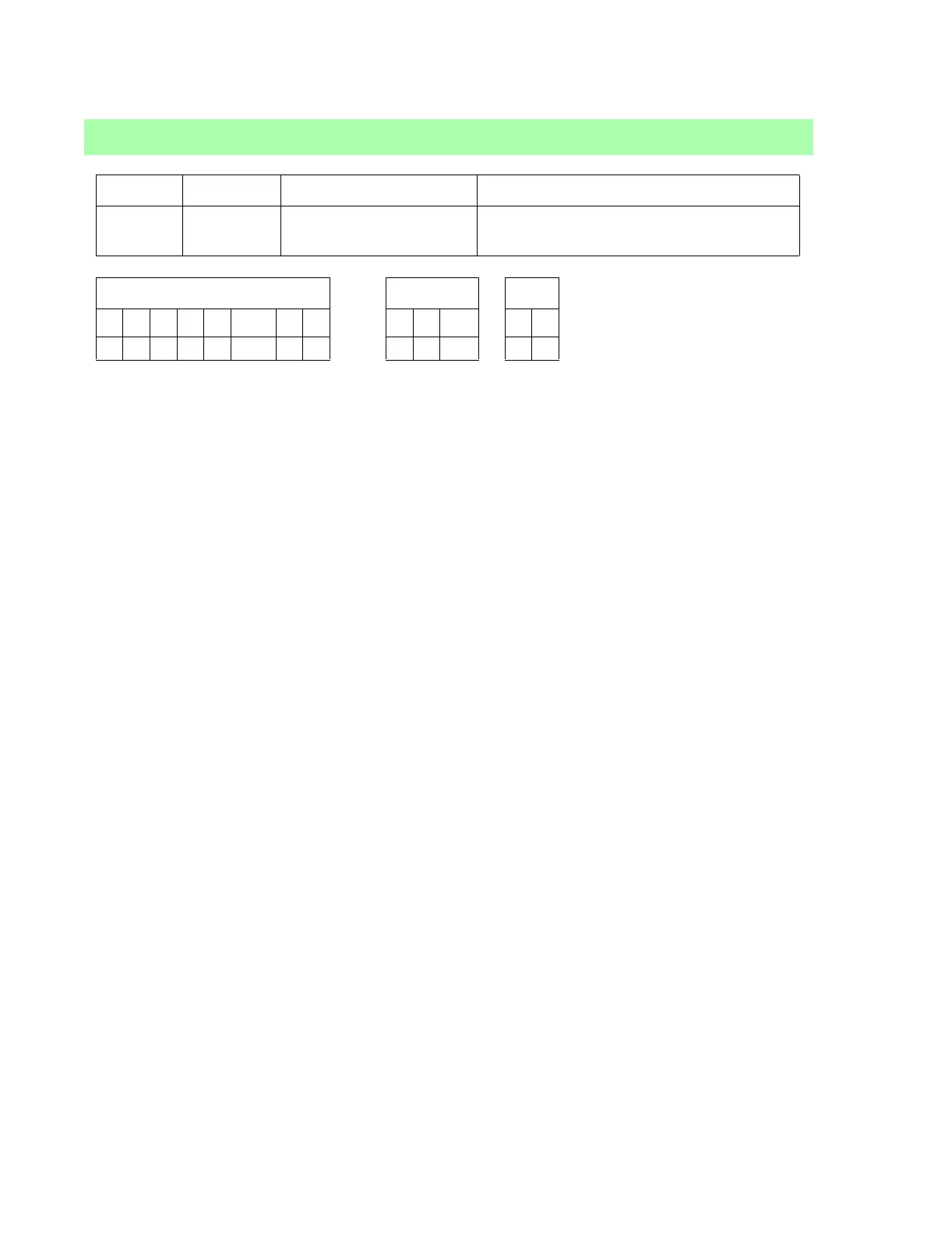

Flags ALTD I/O

S Z L/V C F R SP S D

- - - -

Loading...

Loading...