140 Rabbit 2000/3000 Microprocessor

Description

Arithmetically shifts to the right the bits in the data whose address is

• the data in HL, or

• the sum of the data in IX and a displacement d,or

• the sum of the data in IY and a displacement d.

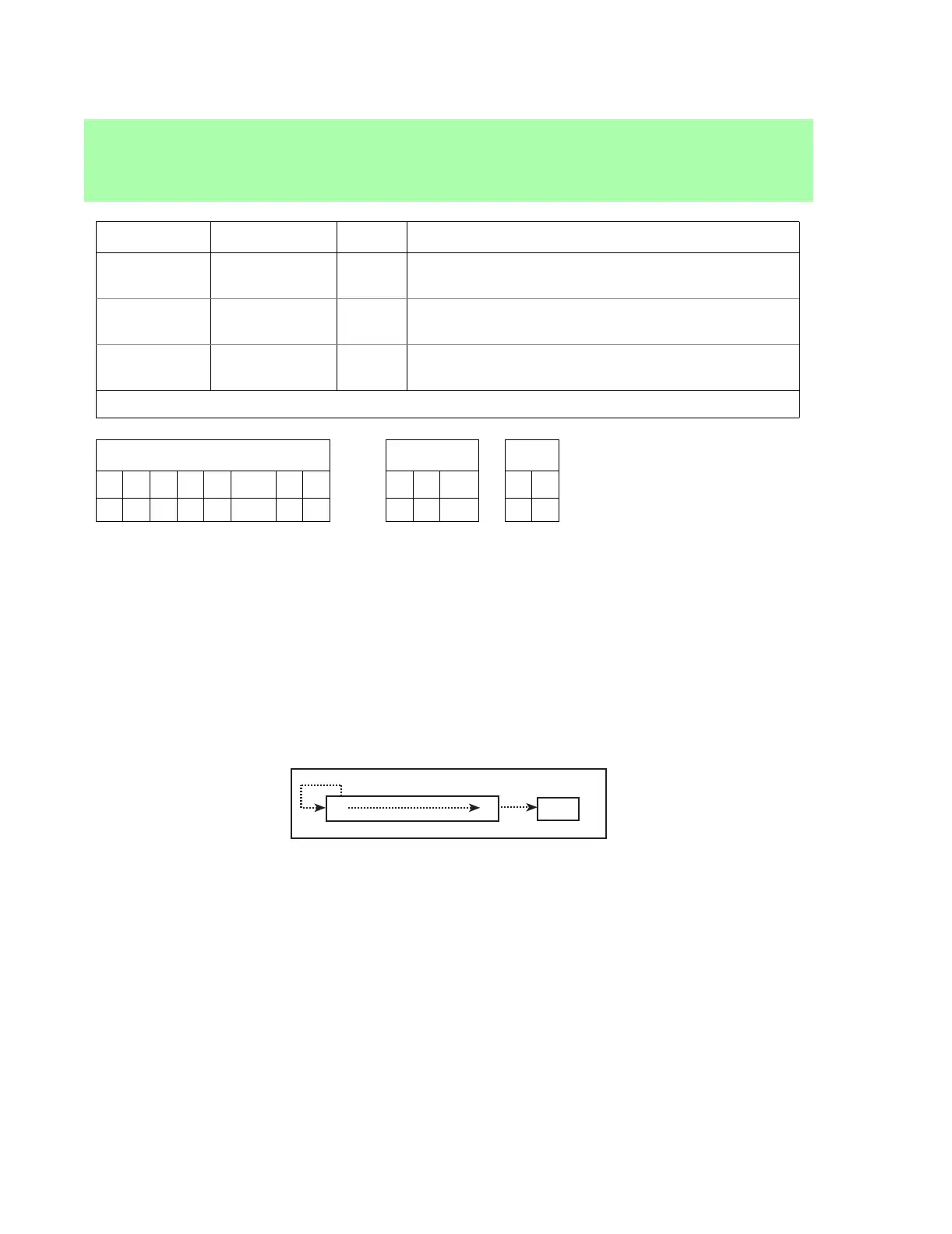

Bits 7 through 1 are shifted to the next lowest-order bit position (bit 7 is shifted to bit 6, etc.). Bit 7 is also cop-

ied to itself. Bit 0 is shifted to the C flag. See figure below.

Figure 8: The bit logic of the SRA instruction.

SRA (HL)

SRA (IX+d)

SRA (IY+d)

Opcode Instruction Clocks Operation

CB 2E SRA (HL) 10* (HL) = {(HL)[7],(HL)[7,1]};

CF = (HL)[0]

DD CB d 2E SRA (IX+d) 13** (IX + d) = {(IX + d)[7],(IX + d)[7,1]};

CF = (IX + d)[0]

FD CB d 2E SRA (IY+d) 13** (IY +d) = {(IY + d)[7],(IY + d)[7,1]};

CF = (IY + d)[0]

Clocking: *10 (2,2,1,2,3) **13 (2,2,2,2,2,3)

Flags ALTD I/O

S Z L/V C F R SP S D

• • L • • • •

7

0

CF

Loading...

Loading...