54 Rabbit 2000/3000 Microprocessor

Description

The Interrupt Priority Register, IP is an 8-bit register that forms a stack of the current priority and the other

previous 3 priorities. IPSET 0 forms the lowest priority; IPSET 3 forms the highest priority. These instruc-

tions are privileged.

• IPSET 0: The IPSET 0 instruction shifts the contents of the register holding the previous pri-

orities 2 bits to the left, then sets the Interrupt Priority Register (bits 0 and 1) to 00.

• IPSET 1: The IPSET 1 instruction first shifts the contents of the register holding the previous

priorities 2 bits to the left, then sets the Interrupt Priority Register (bits 0 and 1) to 01.

• IPSET 2: The IPSET 2 instruction shifts the contents of the register holding the previous pri-

orities 2 bits to the left, then sets the Interrupt Priority Register (bits 0 and 1) to 10.

• IPSET 3: The IPSET 3 instruction shifts the contents of the register holding the previous pri-

orities 2 bits to the left, then sets the Interrupt Priority Register (bits 0 and 1) to 11.

IPSET 0

IPSET 1

IPSET 2

IPSET 3

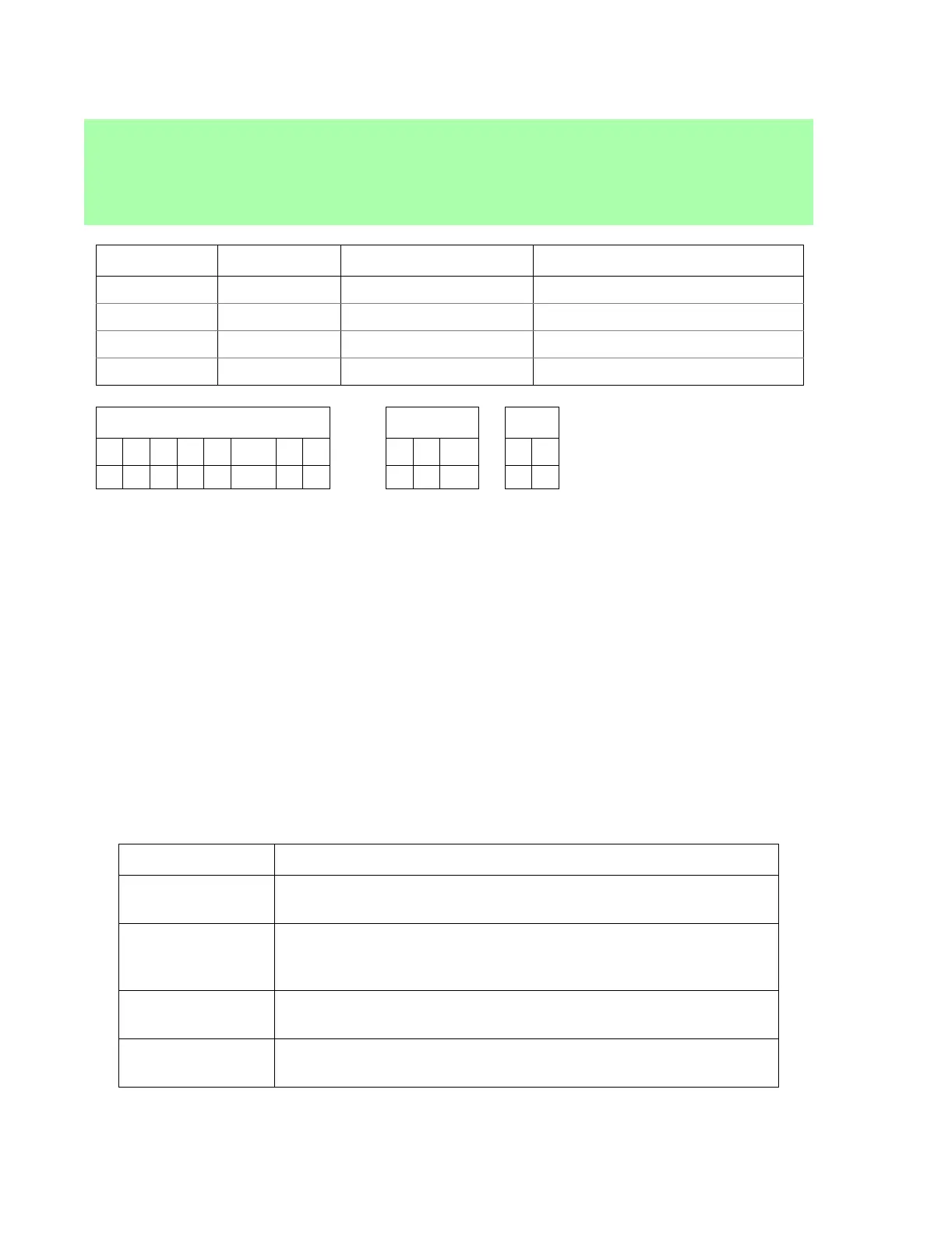

Opcode Instruction Clocks Operation

ED 46 IPSET 0 4 (2,2) IP = {IP[5:0], 00}

ED 56 IPSET 1 4 (2,2) IP = {IP[5:0], 01}

ED 4E IPSET 2 4 (2,2) IP = {IP[5:0], 10}

ED 5E IPSET 3 4 (2,2) IP = {IP[5:0], 11}

Flags ALTD I/O

S Z L/V C F R SP S D

- - - -

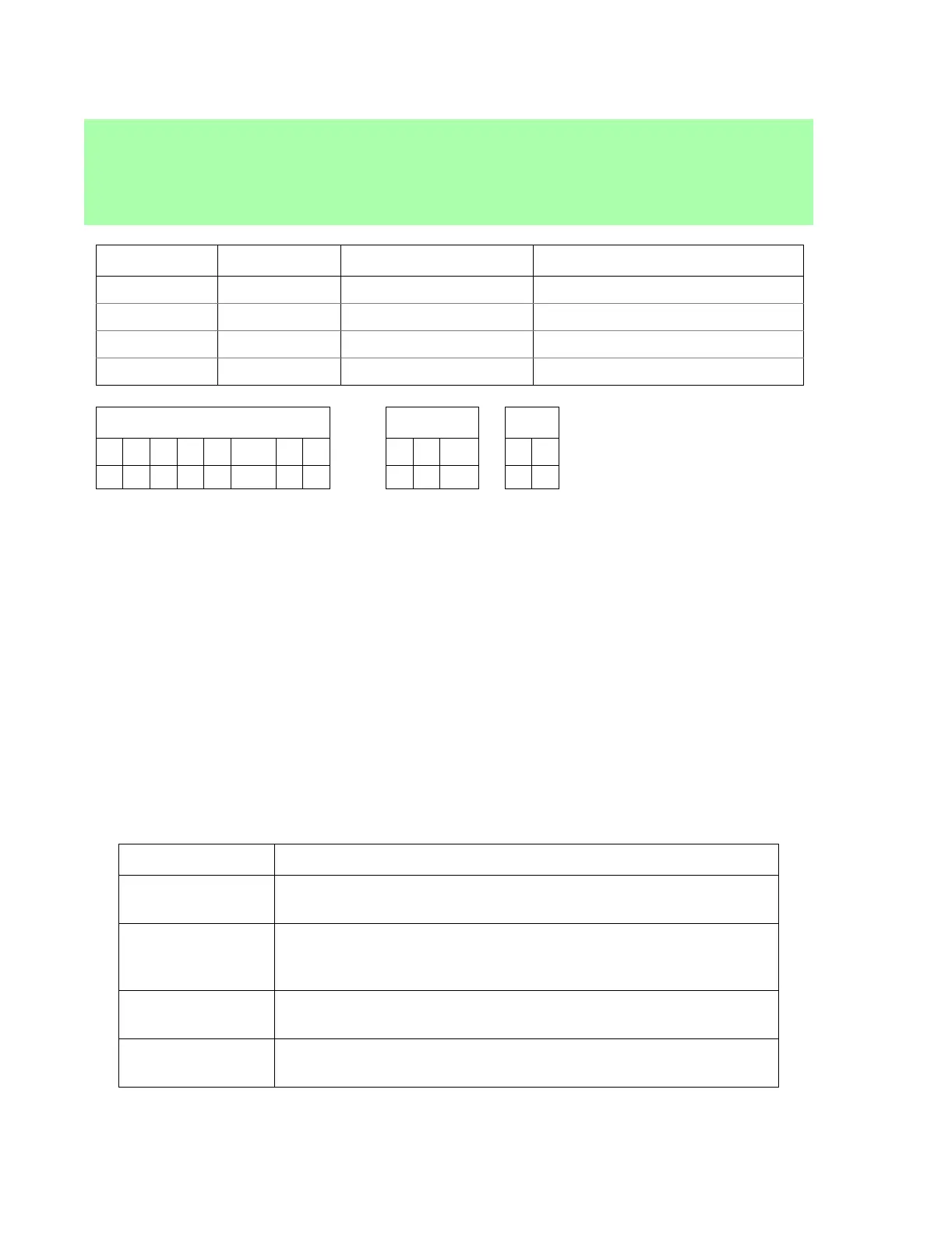

Processor Priority Effect on Interrupts

0 All interrupts, priority 1,2 and 3 take place after

execution of current non privileged instruction.

1 Only interrupts of priority 2 and 3 take place

after execution of current non privileged

instruction.

2 Only interrupts of priority 3 take place after

execution of current non privileged instruction.

3 All interrupts are suppressed

(except the RST instruction).

Loading...

Loading...