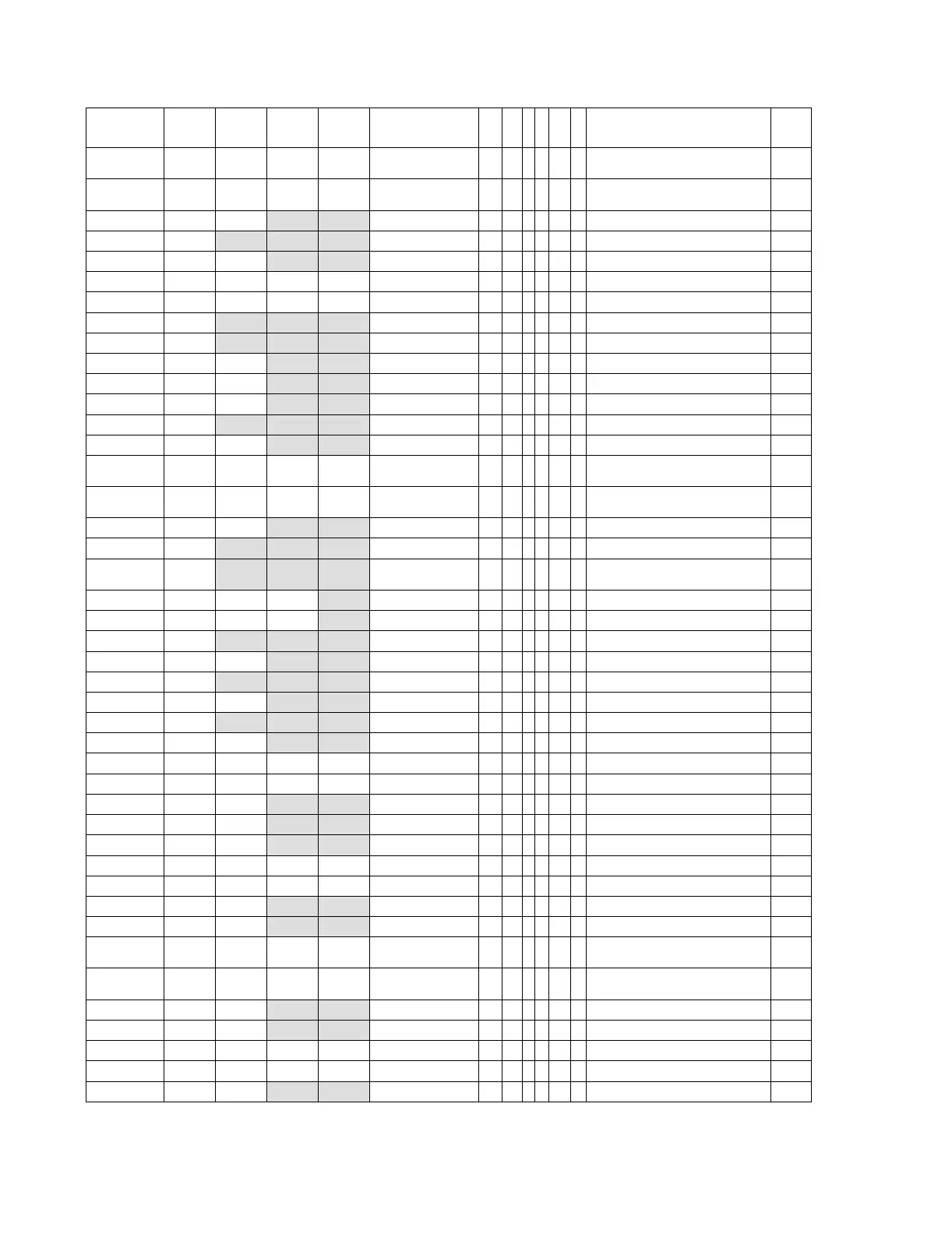

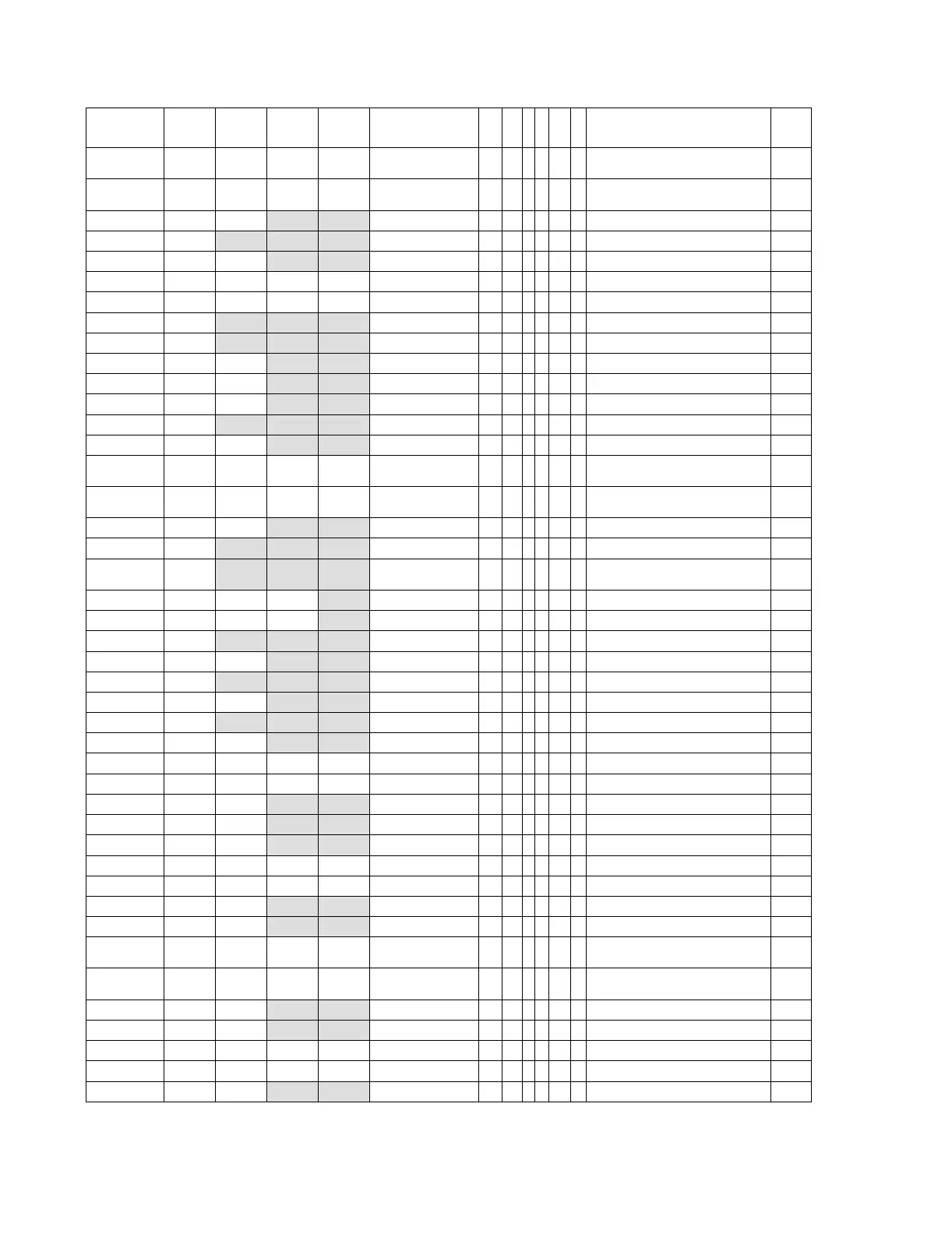

166 Rabbit 2000/3000 Microprocessor

RLC (IX+d) 11011101 11001011 ----d--- 00000110 13 (2,2,2,2,2,3) f b * * L *

(IX+d) = {(IX+d)[6,0],(IX+d)[7]};

CY = (IX+d)[7]

RLC (IY+d) 11111101 11001011 ----d--- 00000110 13 (2,2,2,2,2,3) f b * * L *

(IY+d) = {(IY+d)[6,0],(IY+d)[7]};

CY = (IY+d)[7]

RLC r 11001011 00000-r- 4(2,2) fr * * L * r = {r[6,0],r[7]}; CY = r[7]

RLCA 00000111 2 fr - - - * A = {A[6,0],A[7]}; CY = A[7]

RR (HL) 11001011 00011110 10 (2,2,1,2,3) f b * * L * {(HL),CY} = {CY,(HL)}

RR (IX+d) 11011101 11001011 ----d--- 00011110 13 (2,2,2,2,2,3) f b * * L * {(IX+d),CY} = {CY,(IX+d)}

RR (IY+d) 11111101 11001011 ----d--- 00011110 13 (2,2,2,2,2,3) f b * * L * {(IY+d),CY} = {CY,(IY+d)}

RR DE 11111011 2 fr * * L * {DE,CY} = {CY,DE} N

RR HL 11111100 2 fr * * L * {HL,CY} = {CY,HL} N

RR IX 11011101 11111100 4(2,2) f * * L * {IX,CY} = {CY,IX} N

RR IY 11111101 11111100 4(2,2) f * * L * {IY,CY} = {CY,IY} N

RR r 11001011 00011-r- 4(2,2) fr * * L * {r,CY} = {CY,r}

RRA 00011111 2 fr - - - * {A,CY} = {CY,A}

RRC (HL) 11001011 00001110 10 (2,2,1,2,3) f b * * L * (HL) = {(HL)[0],(HL)[7,1]}; CY = (HL)[0]

RRC (IX+d) 11011101 11001011 ----d--- 00001110 13 (2,2,2,2,2,3) f b * * L *

(IX+d) = {(IX+d)[0],(IX+d)[7,1]};

CY = (IX+d)[0]

RRC (IY+d) 11111101 11001011 ----d--- 00001110 13 (2,2,2,2,2,3) f b * * L *

(IY+d) = {(IY+d)[0],(IY+d)[7,1]};

CY = (IY+d)[0]

RRC r 11001011 00001-r- 4(2,2) fr * * L * r = {r[0],r[7,1]}; CY = r[0]

RRCA 00001111 2 fr - - - * A = {A[0],A[7,1]}; CY = A[0]

RST v 11-v-111 8 (2,2,2,2) - - - -

(SP-1) = PCH; (SP-2) = PCL;

SP = SP - 2; PC = {R, 0, v, 0000}

SBC A,(HL) 11011101 10011110 ----d--- 9 (2,2,2,1,2) fr s * * V * A=A-(IX+d)-CY

SBC (IX+d) 11111101 10011110 ----d--- 9 (2,2,2,1,2) fr s * * V * A=A-(IY+d)-CY

SBC (IY+d) 10011110 5 (2,1,2) fr s * * V * A=A-(HL)-CY

SBC A,n 11011110 ----n--- 4(2,2) fr * * V * A=A-n-CY

SBC A,r 10011-r- 2 fr * * V * A=A-r-CY

SBC HL,ss 11101101 01ss0010 4(2,2) fr * * V * HL = HL - ss - CF

SCF 00110111 2 f - - - 1 CF = 1

SET b,(HL) 11001011 11-b-110 10 (2,2,1,2,3) b - - - - (HL) = (HL) | bit

SET b,(IX+d) 11011101 11001011 ----d--- 11-b-110 13 (2,2,2,2,2,3) b - - - - (IX+d) = (IX+d) | bit

SET b,(IY+d) 11111101 11001011 ----d--- 11-b-110 13 (2,2,2,2,2,3) b - - - - (IY+d) = (IY+d) | bit

SET b,r 11001011 11-b--r- 4(2,2) r - - - - r=r|bit

SETUSR 11101101 01101111 4(2,2) - - - - SU = {SU[5:0], 0x01} P

SLA (HL) 11001011 00100110 10 (2,2,1,2,3) f b * * L * (HL) = {(HL)[6,0],0}; CY = (HL)[7]

SLA (IX+d) 11011101 11001011 ----d--- 00100110 13 (2,2,2,2,2,3) f b * * L * (IX+d) = {(IX+d)[6,0],0}; CY = (IX+d)[7]

SLA (IY+d) 11111101 11001011 ----d--- 00100110 13 (2,2,2,2,2,3) f b * * L * (IY+d) = {(IY+d)[6,0],0}; CY = (IY+d)[7]

SLA r 11001011 00100-r- 4(2,2) fr * * L * r = {r[6,0],0}; CY = r[7]

SRA (HL) 11001011 00101110 10 (2,2,1,2,3) f b * * L * (HL) = {(HL)[7],(HL)[7,1]}; CY = (HL)[0]

SRA (IX+d) 11011101 11001011 ----d--- 00101110 13 (2,2,2,2,2,3) f b * * L *

(IX+d) = {(IX+d)[7],(IX+d)[7,1]}; CY =

(IX+d)[0]

SRA (IY+d) 11111101 11001011 ----d--- 00101110 13 (2,2,2,2,2,3) f b * * L *

(IY+d) = {(IY+d)[7],(IY+d)[7,1]}; CY =

(IY+d)[0]

SRA r 11001011 00101-r- 4(2,2) fr * * L * r = {r[7],r[7,1]}; CY = r[0]

SRL (HL) 11001011 00111110 10 (2,2,1,2,3) f b * * L * (HL) = {0,(HL)[7,1]}; CY = (HL)[0]

SRL (IX+d) 11011101 11001011 ----d--- 00111110 13 (2,2,2,2,2,3) f b * * L * (IX+d) = {0,(IX+d)[7,1]}; CY = (IX+d)[0]

SRL (IY+d) 11111101 11001011 ----d--- 00111110 13 (2,2,2,2,2,3) f b * * L * (IY+d) = {0,(IY+d)[7,1]}; CY = (IY+d)[0]

SRL r 11001011 00111-r- 4(2,2) fr * * L * r = {0,r[7,1]}; CY = r[0]

Instruction

Opcode

byte 1

Opcode

byte 2

Opcode

byte 3

Opcode

byte 4

Clock cycles A I S Z LV C Operation N/M/P

Loading...

Loading...