RZ/A2M SUB Board RTK79210XXB00000BE 3. Operating specifications

R20UT4398EJ0100 Rev.1.00 3-5

2018.10.11

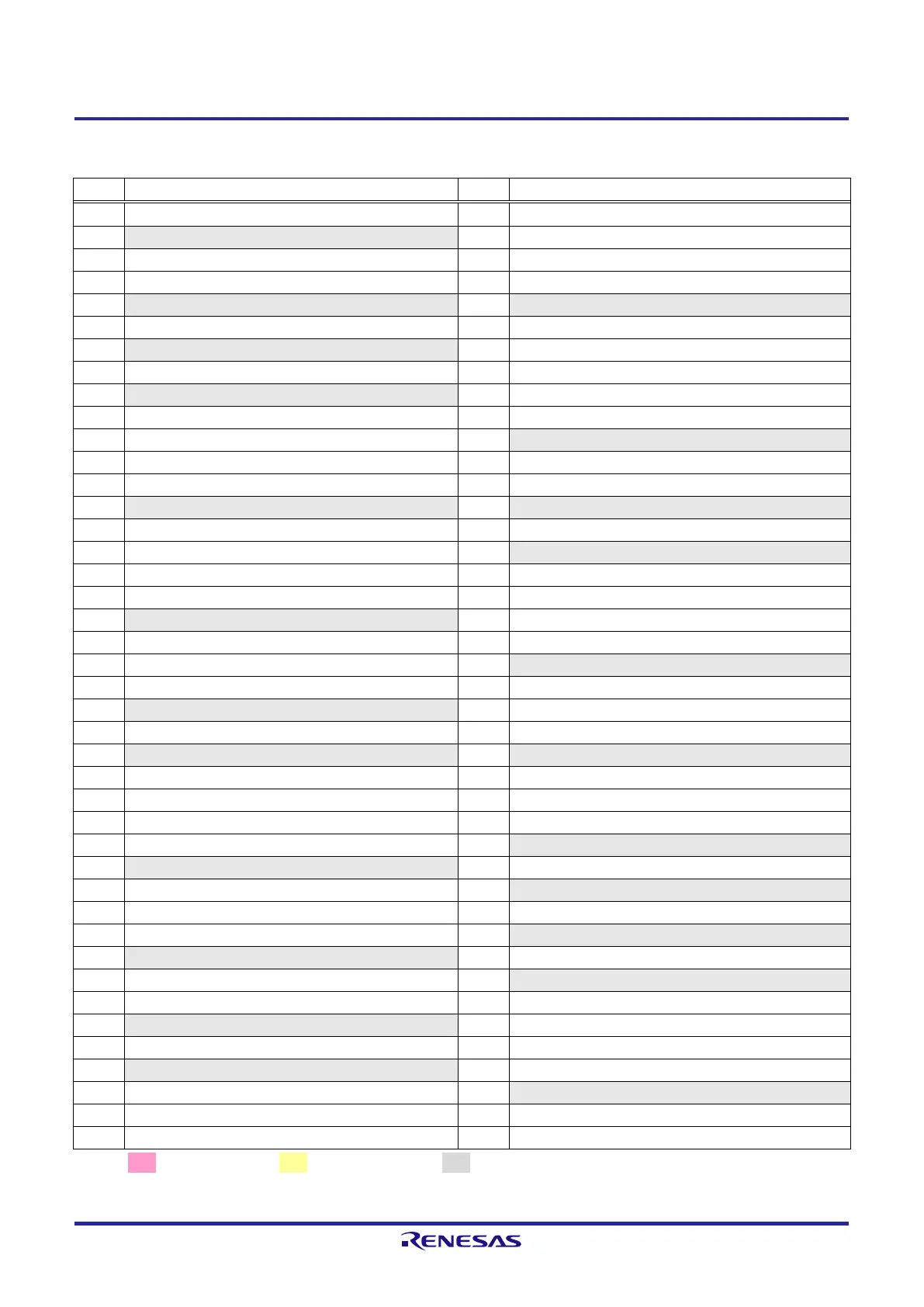

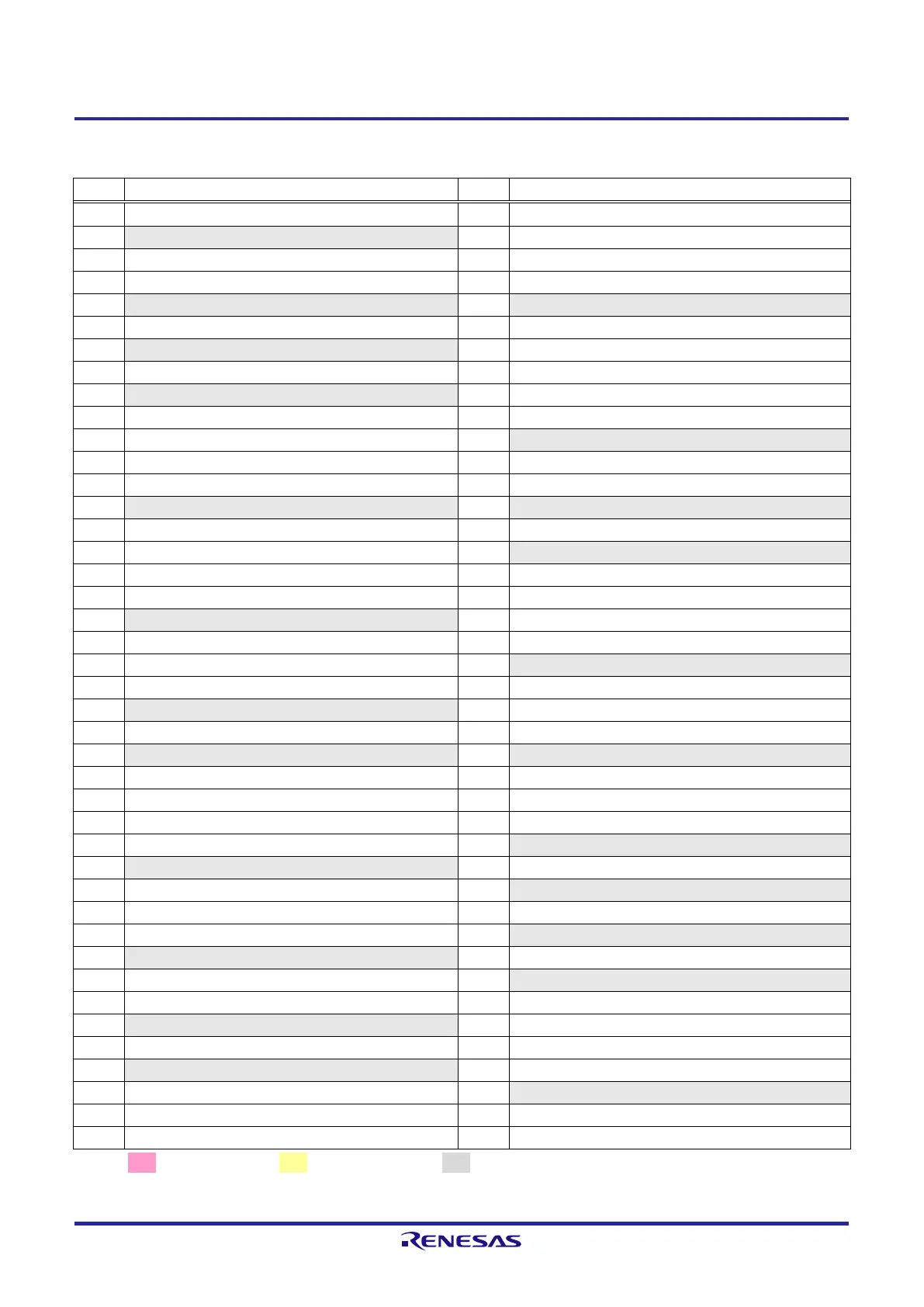

Table 3.1.2 CPU Board Connector (CN1) Pin Layout Table (2)

PE_1 / ET0_RXD0/RMII0_RXD0 / VIO_D7

PA_2 / DV0_DATA11 / LCD0_DATA12

PA_7 / DV0_DATA6 / LCD0_DATA17

PA_0 / DV0_DATA13 / LCD0_DATA10

PE_2 / ET0_RXD1/RMII0_RXD1 / VIO_D6

PE_3 / ET0_RXER/RMII0_RXER / VIO_D5

PA_1 / DV0_DATA12 / LCD0_DATA11

P8_0 / DV0_DATA14 / LCD0_DATA9

P8_7 / A7 / DRP17 / RSPCK0

PF_1 / DV0_DATA16 / LCD0_DATA7

PF_0 / DV0_DATA15 / LCD0_DATA8

PE_4 / ET0_CRS/RMII0_CRSDV / VIO_D4

P8_5 / A5 / DRP19 / MISO0

PF_2 / DV0_DATA17 / LCD0_DATA6

P8_6 / A6 / DRP18 / MOSI0

P8_4 / A4 / DRP20 / SSL00

PE_0 / ET0_RXCLK/REF50CK0 / VIO_FLD

P6_2 / ET0_TXD0/RMII0_TXD0 / VIO_VD

PF_6 / DV0_DATA21 / LCD0_DATA2

PK_0 / ET1_TXEN/RMII1_TXDEN / NAF3

P6_3 / ET0_TXD1/RMII0_TXD1 / VIO_HD

P9_4 / A12 / DRP12 / SSITxD0

PF_4 / DV0_DATA19 / LCD0_DATA4

PF_5 / DV0_DATA20 / LCD0_DATA3

P6_1 / ET0_TXEN/RMII0_TXDEN / VIO_CLK

P7_4 / CAS / DRP07 / RTS1

P7_1 / RD/WR / DRP05 / RxD1

PF_3 / DV0_DATA18 / LCD0_DATA5

PK_3 / ET1_RXCLK/REF50CK1 / NAF6

PK_2 / ET1_TXD1/RMII1_TXD1 / NAF5

PF_7 / DV0_DATA23 / LCD0_DATA0

PK_1 / ET1_TXD0/RMII1_TXD0 / NAF4

PJ_7 / NAF0 / LCD0_EXTCLK

PH_2 / DV0_DATA22 / LCD0_DATA1

P3_2 / ET1_CRS/RMII1_CRSDV / FRE

P3_5 / ET1_RXD1/RMII1_RXD1 / FCLE

[Note] : 5V power source, : 3.3V power source, : GND

Loading...

Loading...