RZ Family / RZ/G, RZ/A Series 2. Functional Specifications

R01UH0990EJ0101 Rev.1.01 Page 28 of 83

Jul 28, 2022

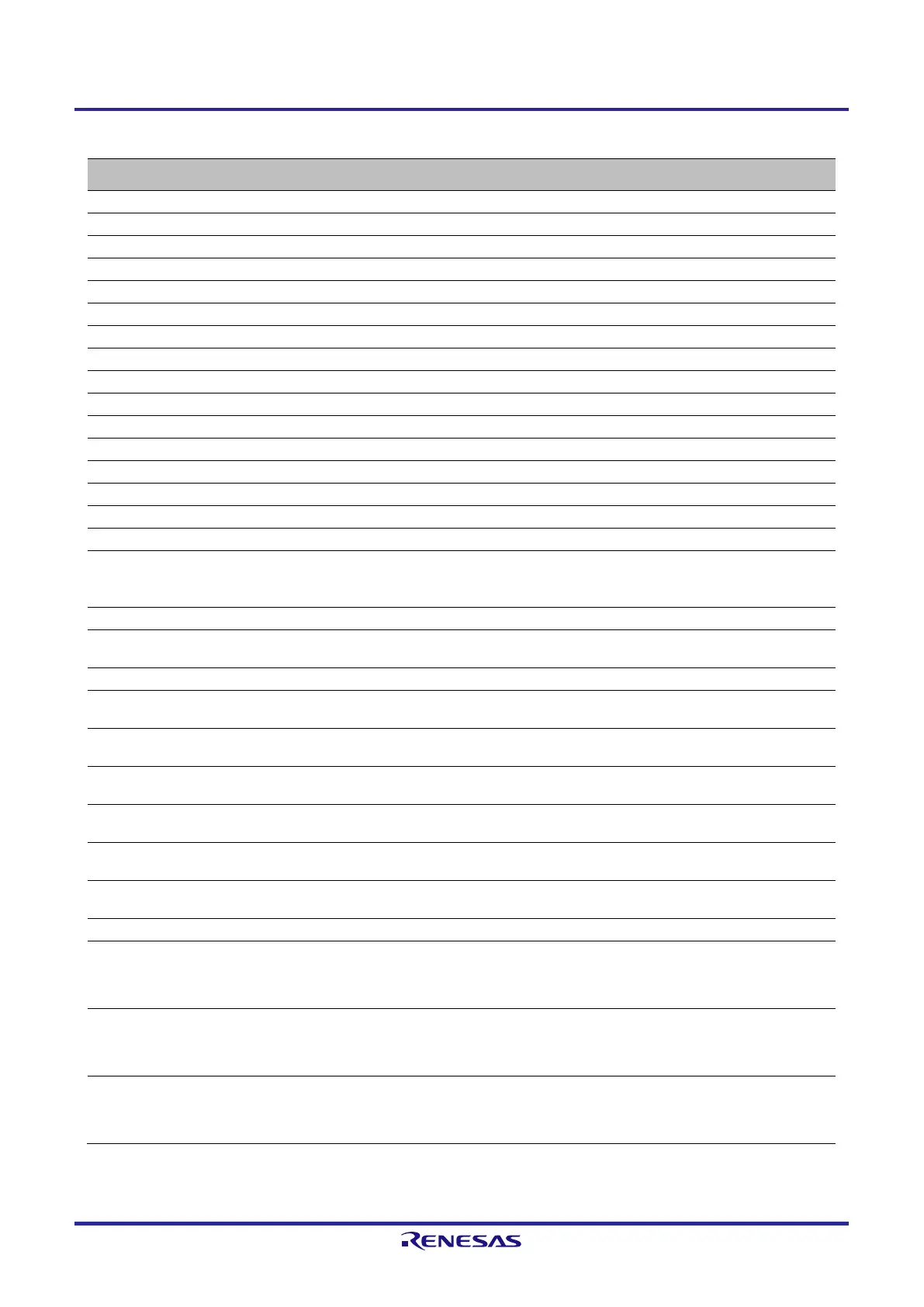

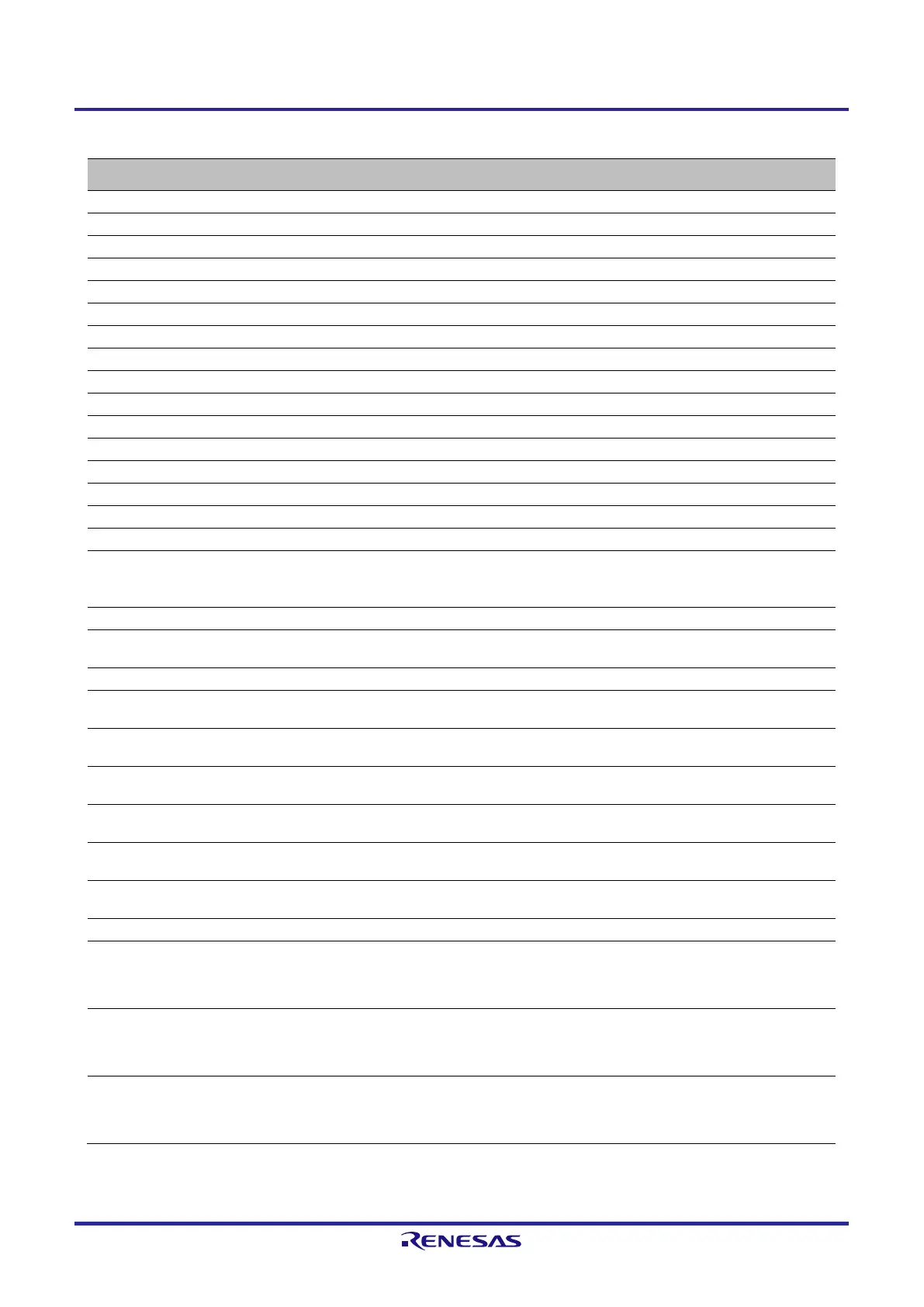

Table 2.2 List of Pin Function Selection Used on Each Module Board (4/18)

Input controlling PVDD182533_0

power level with SW1-3

High: 3.3V, Low: 1.8V

24MHz input, connected to clock

generator (IC31) for system clock

Input BOOT_SEL0#, BOOT_SEL1#

and BOOT_SEL2# logic states

Input BOOT_SEL0#, BOOT_SEL1#

and BOOT_SEL2# logic states

Input BOOT_SEL0#, BOOT_SEL1#

and BOOT_SEL2# logic states

Initial setting: 1 (Pull Up), should be

controllable by resistor.

Initial setting: 0 (Pull Down), should

be controllable by resistor.

Initial setting: 0 (Pull Down), should

be controllable by resistor.

OctaRAM (IC3)

Note: Unused in case of

RZ/G2UL

OctaFlash (IC2) and OctaRAM (IC3)

Note: Unused in case of

RZ/G2UL

OctaFlash (IC2) and OctaRAM (IC3)

Note: Unused in case of

RZ/G2UL

Loading...

Loading...