14

CDX-MP80

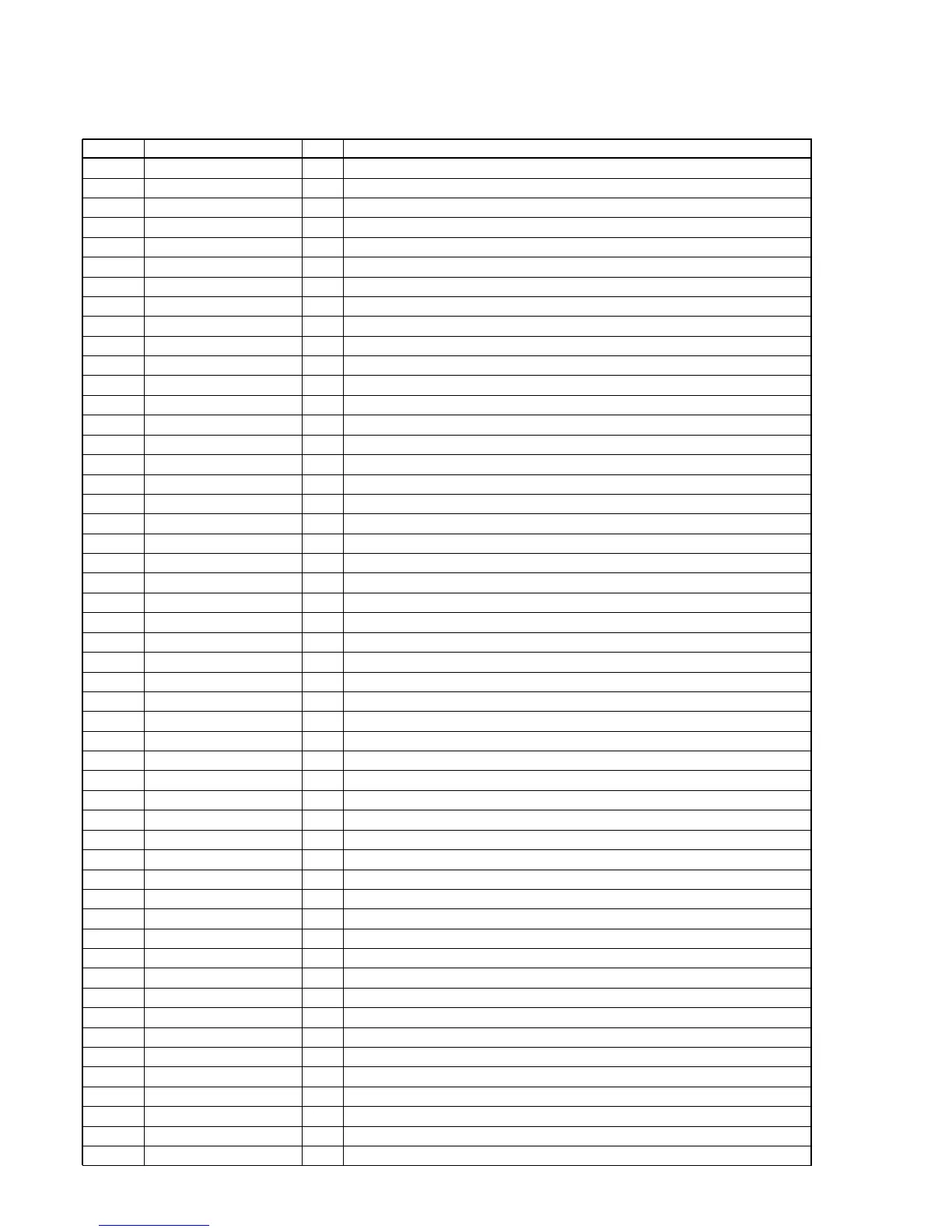

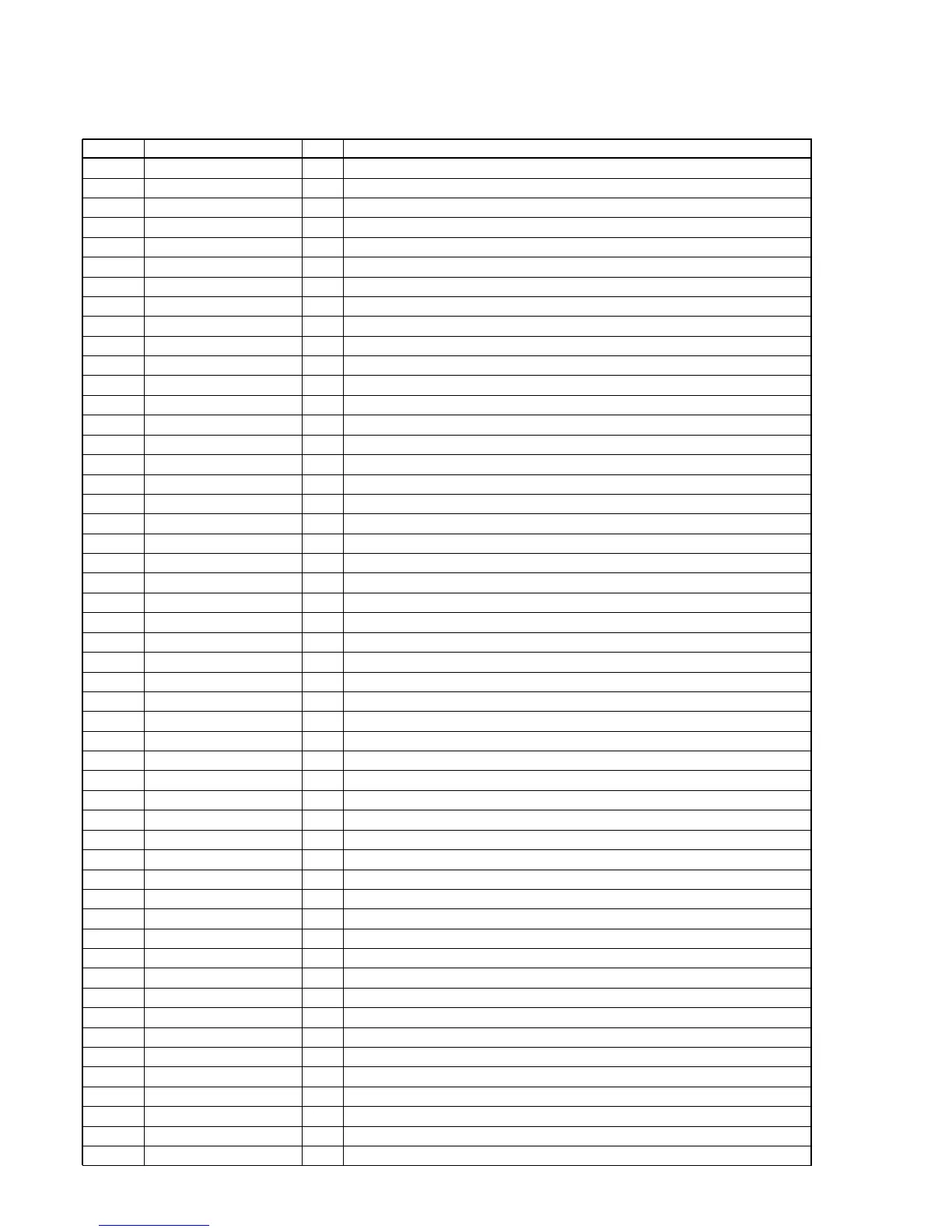

4-1. IC PIN DESCRIPTIONS

• IC5 CXD9684R-004 (AUDIO INTERFACE) (SERVO BOARD)

Pin No. Pin Name I/O Pin Description

1 RESET I Reset input

2MIMD I CPU interface mode select signal input Connecting to +3.3 V in this set.

3 AD0 I CPU interface chip select signal input

4 AD1 I CPU interface latch pulse signal input

5 MIDIO (I2C SDA) I/O CPU interface data input/output

6 MICK (I2C SCL) I CPU interface clock signal input

7 AD2 I CPU interface acknowledge signal input

8 VDDT (3.3V) — Power supply pin (+3.3 V)

9 SDO O Data output

10 AD3 O Bit output

11 AD4 O LR clock output

12 SDI0 I Data input 0

13 BCKIA I Bit clock input A

14 LRCKIA I LR clock input A

15 AD5 I Data input 1

16 CE I Bit clock input B

17 OE I LR clock input B

18 VDD (2.5V) — Power supply pin (+2.5 V)

19 STANDBY I Standby mode control signal input

20 VSS (2.5GND) — Ground pin

21 VSSL (2.5GND) — Ground pin for DAC Lch

22 VRAL — Reference voltage pin for DAC Lch

23 LO O DAC Lch output

24 VDAL (2.5V) — Power supply pin (+2.5 V) for DAC Lch

25 VDAR (2.5V) — Power supply pin (+2.5 V) for DAC Rch

26 RO O DAC Rch output

27 VRAR — Reference voltage pin for DAC Rch

28 VSSR (2.5GND) — Ground pin for DAC Rch

29 TESTP I Test pin

30 CKS I VCO select signal input

31 AD12 O Address output 0

32 AD11 O Address output 1

33 AD10 O Address output 2

34 AD9 O Address output 3

35 VDDT (3.3V) — Power supply pin (+3.3 V)

36 AD8 O Address output 4

37 AD7 O Address output 5

38 AD6 O Address output 6

39 PO7 O Address output 7

40 VSS — Ground pin

41 AD13 I Flag input 0

42 AD14 I Flag input 1

43 WR I Flag input 2

44 AD16 I Flag input 3

45 AD15 I/O External interrupt signal input/output

46 IO0 I Data input 0

47 IO1 I Data input 1

48 VSS — Ground pin

49 IO2 I Data input 2

50 IO3 I Data input 3

51 IO4 I Data input 4

SECTION 4

DIAGRAMS

Loading...

Loading...