HT-NT3

67

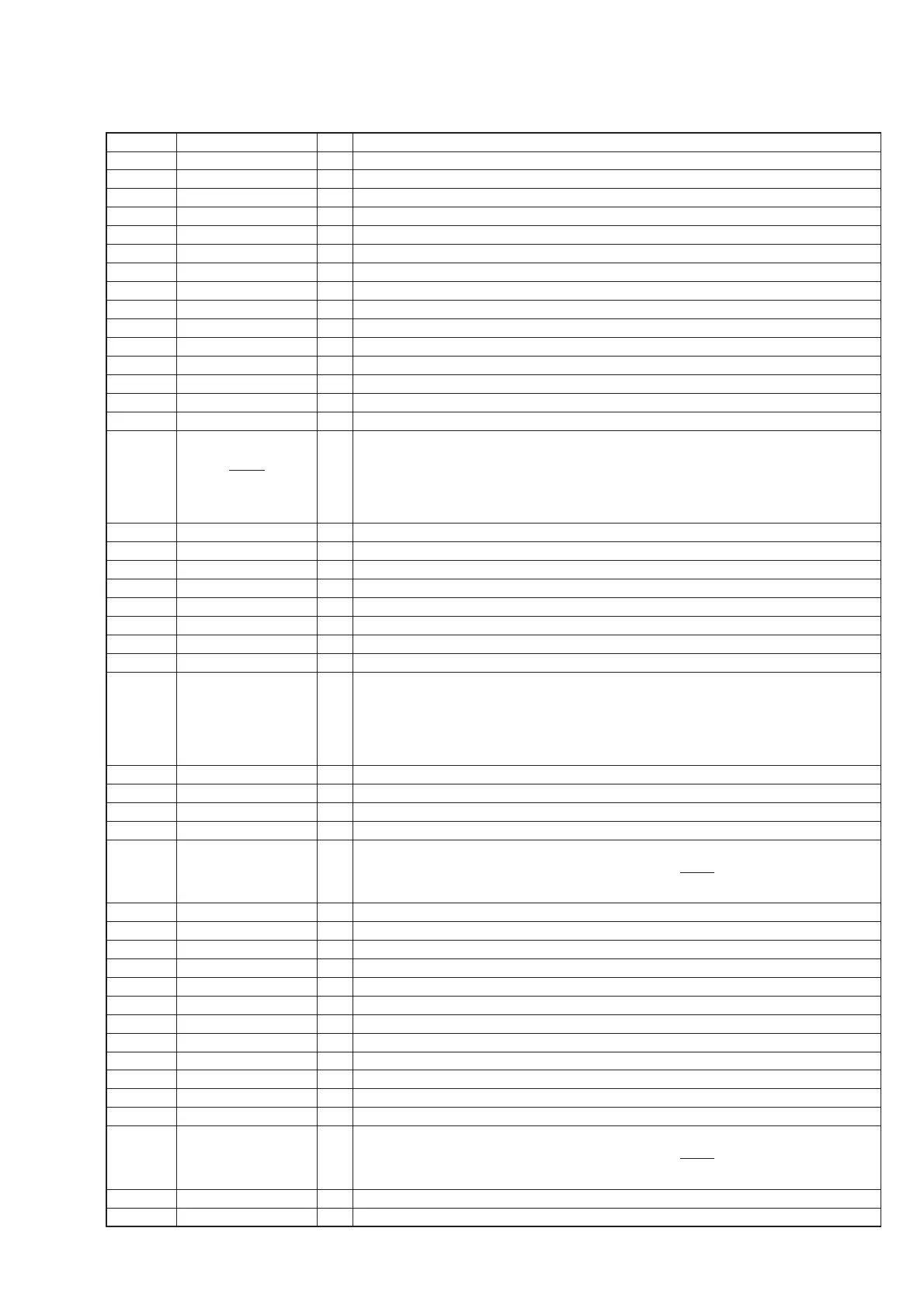

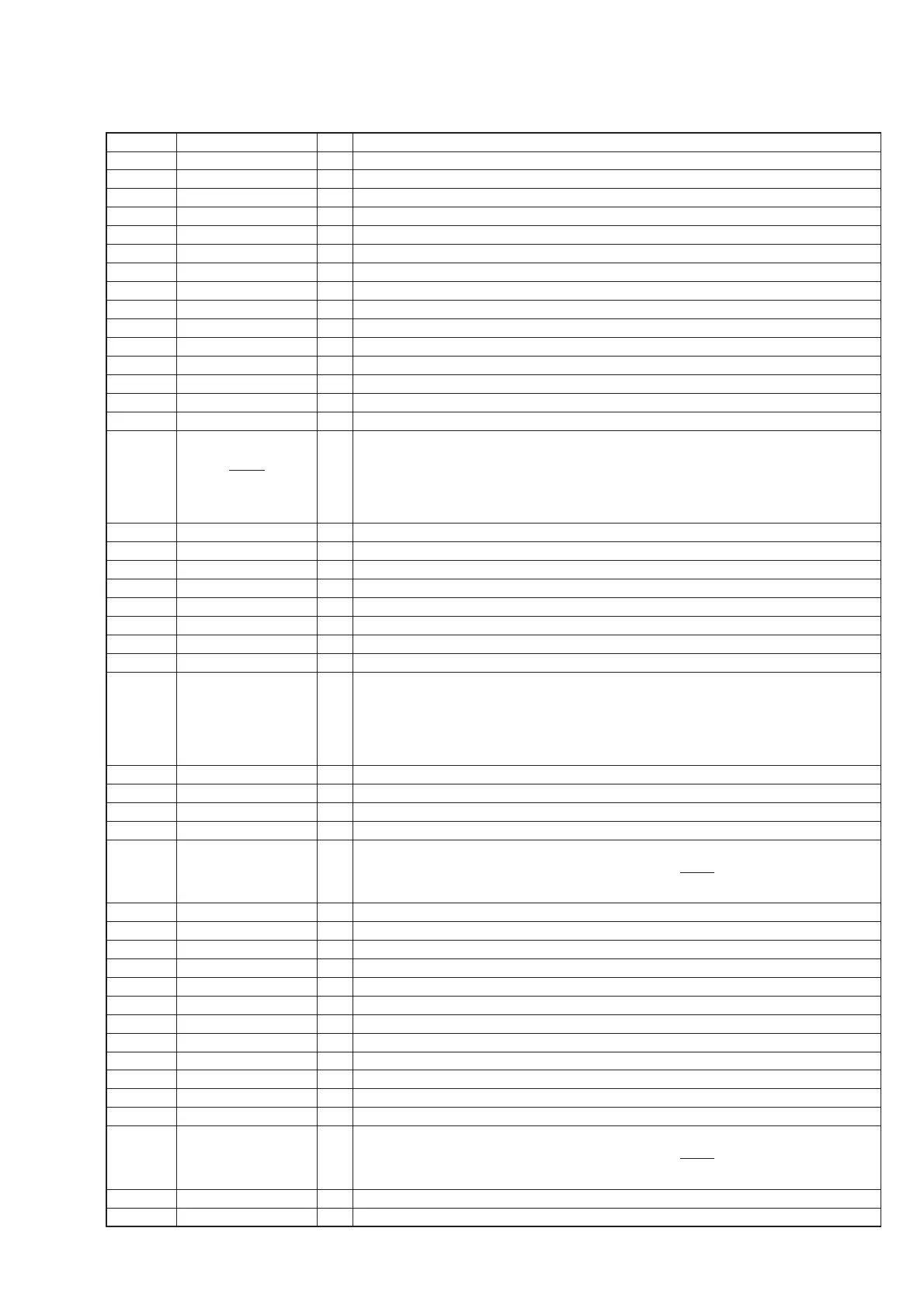

Pin No. Pin Name I/O Description

A1 VDDQ - DQ Power Supply: 1.5V +/-0.075V

A2 DQU5 I/O Data Input/output: Bi-directional data bus.

A3 DQU7 I/O Data Input/output: Bi-directional data bus.

A4 NO_USE - Not used

A5 NO_USE - Not used

A6 NO_USE - Not used

A7 DQU4 I/O Data Input/output: Bi-directional data bus.

A8 VDDQ - DQ Power Supply: 1.5V +/-0.075V

A9 VSS - Ground

B1 VSSQ - DQ Ground

B2 VDD - Power Supply: 1.5V +/-0.075

B3 VSS - Ground

B4 NO_USE - Not used

B5 NO_USE - Not used

B6 NO_USE - Not used

B7

DQSU I/O

Data Strobe: Output with read data, input with write data. Edge-aligned with read data, cen-

tered in write data. For the x16, DQSL: corresponds to the data on DQL0-DQL7; DQSU corre-

sponds to the data on DQU0-DQU7. The data strobe DQS, DQSL and DQSU are paired with

differential signals DQS, DQSL and DQSU, respectively, to provide differential pair signaling to

the system during reads and writes. DDR3 SDRAM supports differential data strobe only and

does not support single-ended.

B8 DQU6 I/O Data Input/output: Bi-directional data bus.

B9 VSSQ - DQ Ground

C1 VDDQ - DQ Power Supply: 1.5V +/-0.075V

C2 DQU3 I/O Data Input/output: Bi-directional data bus.

C3 DQU1 I/O Data Input/output: Bi-directional data bus.

C4 NO_USE - Not used

C5 NO_USE - Not used

C6 NO_USE - Not used

C7 DQSU I/O

Data Strobe: Output with read data, input with write data. Edge-aligned with read data, cen-

tered in write data. For the x16, DQSL: corresponds to the data on DQL0-DQL7; DQSU corre-

sponds to the data on DQU0-DQU7. The data strobe DQS, DQSL and DQSU are paired with

differential signals DQS, DQSL and DQSU, respectively, to provide differential pair signaling to

the system during reads and writes. DDR3 SDRAM supports differential data strobe only and

does not support single-ended.

C8 DQU2 I/O Data Input/output: Bi-directional data bus.

C9 VDDQ - DQ Power Supply: 1.5V +/-0.075V

D1 VSSQ - DQ Ground

D2 VDDQ - DQ Power Supply: 1.5V +/-0.075V

D3 DMU I

Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is

sampled HIGH coincident with that input data during a Write access. DM is sampled on both

edges of DQS. For x8 device, the function of DM or TDQS/ TDQS is enabled by Mode Register

A11 setting in MR1.

D4 NO_USE - Not used

D5 NO_USE - Not used

D6 NO_USE - Not used

D7 DQU0 I/O Data Input/output: Bi-directional data bus.

D8 VSSQ - DQ Ground

D9 VDD - Power Supply: 1.5V +/-0.075

E1 VSS - Ground

E2 VSSQ - DQ Ground

E3 DQL0 I/O Data Input/output: Bi-directional data bus.

E4 NO_USE - Not used

E5 NO_USE - Not used

E6 NO_USE - Not used

E7 DML I

Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is

sampled HIGH coincident with that input data during a Write access. DM is sampled on both

edges of DQS. For x8 device, the function of DM or TDQS/ TDQS is enabled by Mode Register

A11 setting in MR1.

E8 VSSQ - DQ Ground

E9 VDDQ - DQ Power Supply: 1.5V +/-0.075V

MB-1407 BOARD (1/12) IC102, IC103 K4B2G1646Q-BCMA (DDR 3 RAM)

Loading...

Loading...