Power supplies

10/29 AN2586 Rev 8

2.3.2 Programmable voltage detector (PVD)

You can use the PVD to monitor the V

DD

power supply by comparing it to a threshold

selected by the PLS[2:0] bits in the Power control register (PWR_CR).

The PVD is enabled by setting the PVDE bit.

A PVDO flag is available, in the Power control/status register (PWR_CSR), to indicate

whether V

DD

is higher or lower than the PVD threshold. This event is internally connected to

EXTI Line16 and can generate an interrupt if enabled through the EXTI registers. The PVD

output interrupt can be generated when V

DD

drops below the PVD threshold and/or when

V

DD

rises above the PVD threshold depending on the EXTI Line16 rising/falling edge

configuration. As an example the service routine can perform emergency shutdown tasks.

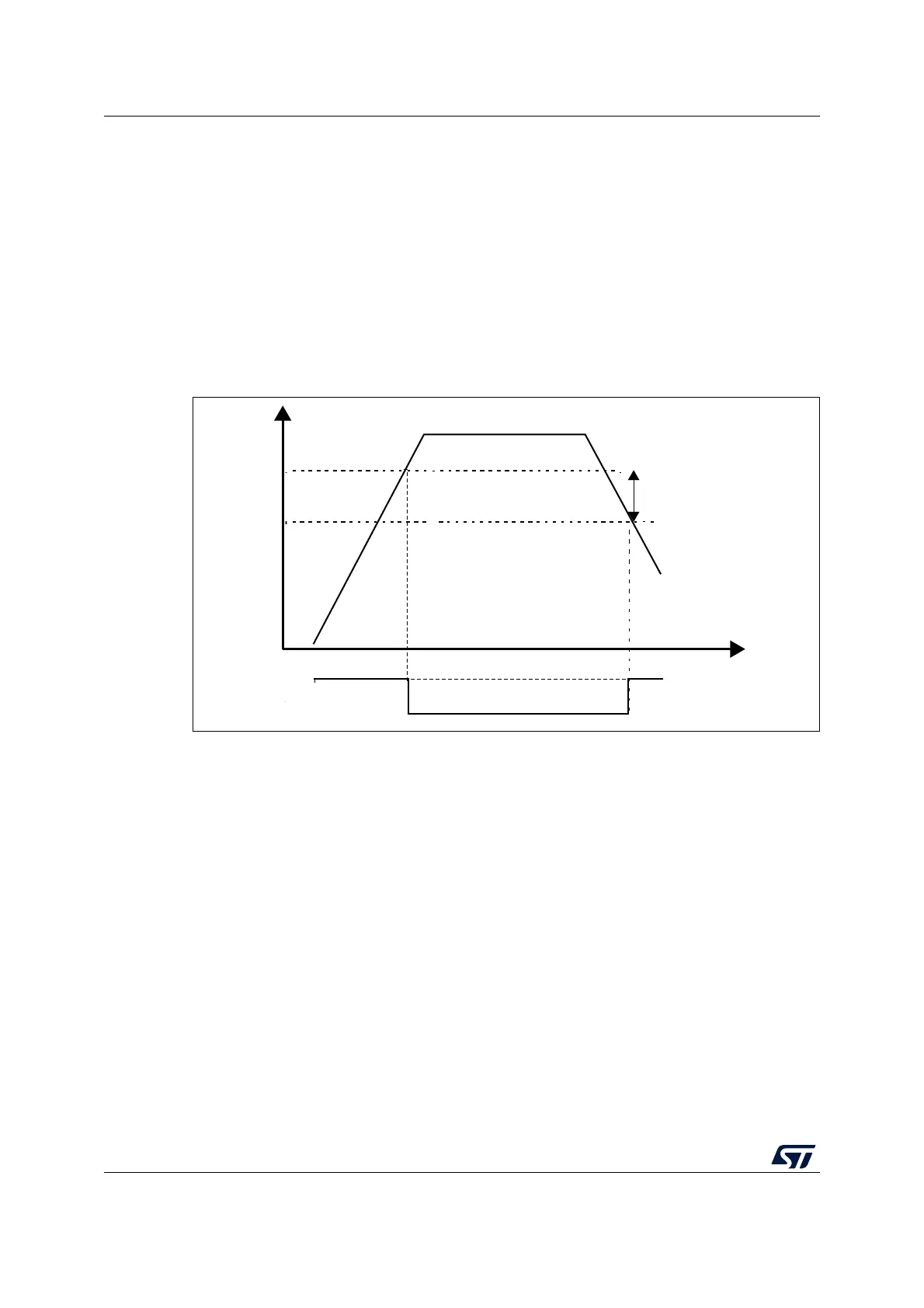

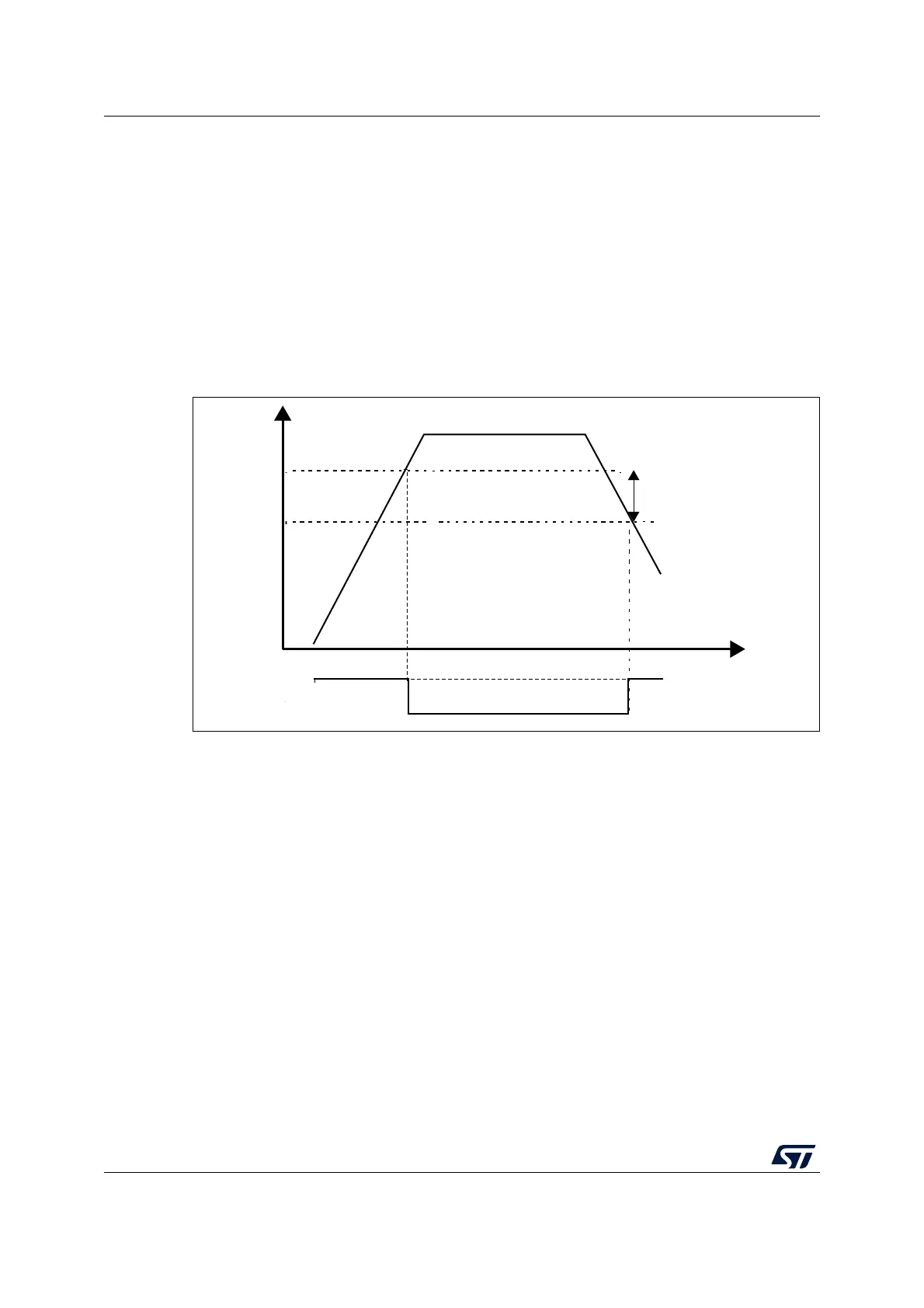

Figure 4. PVD thresholds

2.3.3 System reset

A system reset sets all registers to their reset values except for the reset flags in the clock

controller CSR register and the registers in the Backup domain (see Figure 1).

A system reset is generated when one of the following events occurs:

1. A low level on the NRST pin (external reset)

2. Window watchdog end-of-count condition (WWDG reset)

3. Independent watchdog end-of-count condition (IWDG reset)

4. A software reset (SW reset)

5. Low-power management reset

The reset source can be identified by checking the reset flags in the Control/Status register,

RCC_CSR.

MS30432V2

100 mV

hysteresis

PVD threshold

PVD output

Loading...

Loading...