Chapter 2: Installation

2-25

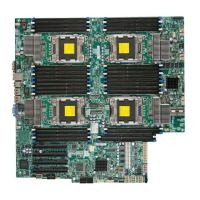

JLAN1JLAN2

14

JUIDB1

JSTBY1

1

3

JIPMB1

JI2C1

1

5

Socket R

LGA 2011

CPU

DESIGNED IN USA

SXB2

SXB1B

1

JD1

JPWR1

1

T-SGPIO4

7

1

T-SGPIO3

7

1

T-SGPIO1

8

7

2

1

T-SGPIO2

87

1

JF1

1

2

19

20

JUSBKM

24

SXB1A

SAS2

SAS1

SAS3

SAS4

J17

H-HS2_2

SP1

JBT1

BD1

A

C

LED2

LE2

LE1

BT1

+

JOH1

JL1

1

R136

JVGA1

JTPM1

J26

J23

1

JCOM1

FAN5

FAN4

4

FAN3

FAN2

FAN1

JWF1

1

J4

J2

J3

J1

C241

JWP1

3

JI2C3

JI2C2

1

3

JPG1

JPB1

JP3

JPME1

JWD

JPL1

1

3

SXB1B: LEFT_WIO_MIDDLE

SXB2: RIGHT_WIO

SXB1A: LEFT_WIO_UP

WRITE PROTECT

JWP1:

USB

USB

1-2:RST

2-3:NIMI

JWD:

JI2C2/JI2C3

1-2:Enable

2-3:Disable

JPMB

OFF:NORMAL

ON:ME RECOVERY

JPME1:

VGA

UID

JTPM1: TPM/PORT80

DIMM4A

DIMM4B

DIMM3B

DIMM3A

KB/MOUSEUSB/2/3

JTPM1:TPM/PORT80

JSTBY1:STAND BY POWER FOR DOM

2-3:NMI

1-2:RST(DEFAULT)

JWD:WATCH DOG TIMER

JD1:

4-7:SPEAKER

1-2:PWR_LED

IPMI LAN

USB/0/1

1-2:ENABLE

2-3:DISABLE

JPL2:LAN2

JPL1:LAN1

2-3:DISABLE

1-2:ENABLE

JPB1: BMC

COM1

JBT1:CMOS CLEAR

LAN2

JL1

LAN1

DIMM2B

DIMM2A

JI2C1

2-3:Disable

1-2:Enable

JOH1:OVER HEAT LED

CPU

OFF:Disable

ON:Enable

2-3:DISABLE

1-2:ENABLE

:CHASSIS INTRUSION

I-SATA3

I-SATA4

I-SATA2

I-SATA1

I-SATA0

I-SATA5

DIMM1B

DIMM1A

JPG1: VGA

J29

1

3

J30

1

3

CPU1

CLOSE 1st

OPEN 1st

C

Serial_Link-SGPIO

Pin Denitions

Pin# Denition Pin Denition

1 NC 2 NC

3 Ground 4 DATA Out

5 Load 6 Ground

7 Clock 8 NC

NC: No Connections

A. T-SGPIO 1

B. T-SGPIO 2

C. T-SGPIO 3

A

B

T-SGPIO 1/2 & 3-SGPIO 1/2 Headers

Two T-SGPIO (Serial-Link General Pur-

pose Input/Output) headers are located

next to the I-SATA Ports on the mother-

board. Additionally, two 3-SGPIO ports

(for SAS) are also located next to USB

8/9 . These headers are used to com-

municate with the enclosure manage-

ment chip in the system. See the table

on the right for pin denitions. Refer to

the board layout below for the locations

of the headers.

Trusted Platform Module Header

Pin Denitions

Pin # Denition Pin # Denition

1 LCLK 2 GND

3 LFRAME 4 No Pin

5 LRESET 6 VCC5

7 LAD3 8 LAD2

9 VCC3 10 LAD1

11 LAD0 12 GND

13 RSV0 14 RSV1

15 SB3V 16 SERIRQ

17 GND 18 CLKRUN

19 LPCPD 20 RSV2

TPM Header (JTPM1)

This header is used to connect a

Trusted Platform Module (TPM), which

is available from a third-party vendor.

A TPM is a security device that sup-

ports encryption and authentication

in hard drives. It enables the moth-

erboard to deny access if the TPM

associated with the hard drive is not

installed in the system. See the table

on the right for pin denitions.

D

E

D. T-SGPIO 4

E. TPM Header

Loading...

Loading...