Specifications

Table 6: Trigger specifications (cont.)

Characteristic Description

Video trigger

formats and fi eld

rates

Triggers from negative sync composite video, field 1 or field 2 for interlaced systems, any field, specific

line, or any line for interlaced or non-interlaced systems. Supported systems include NTSC, PAL,

SECAM.

Standard Video formats are: Trigger on 480p/60, 576p/50, 720p/30, 720p/50, 720p/60, 875i/60,

1080i/50, 1080i/60, 1080p/24, 1080p/24sF, 1080p/25, 1080p/30, 1080p/50, 1080p/60, and custom

bi-level and tri-level sync video standards.

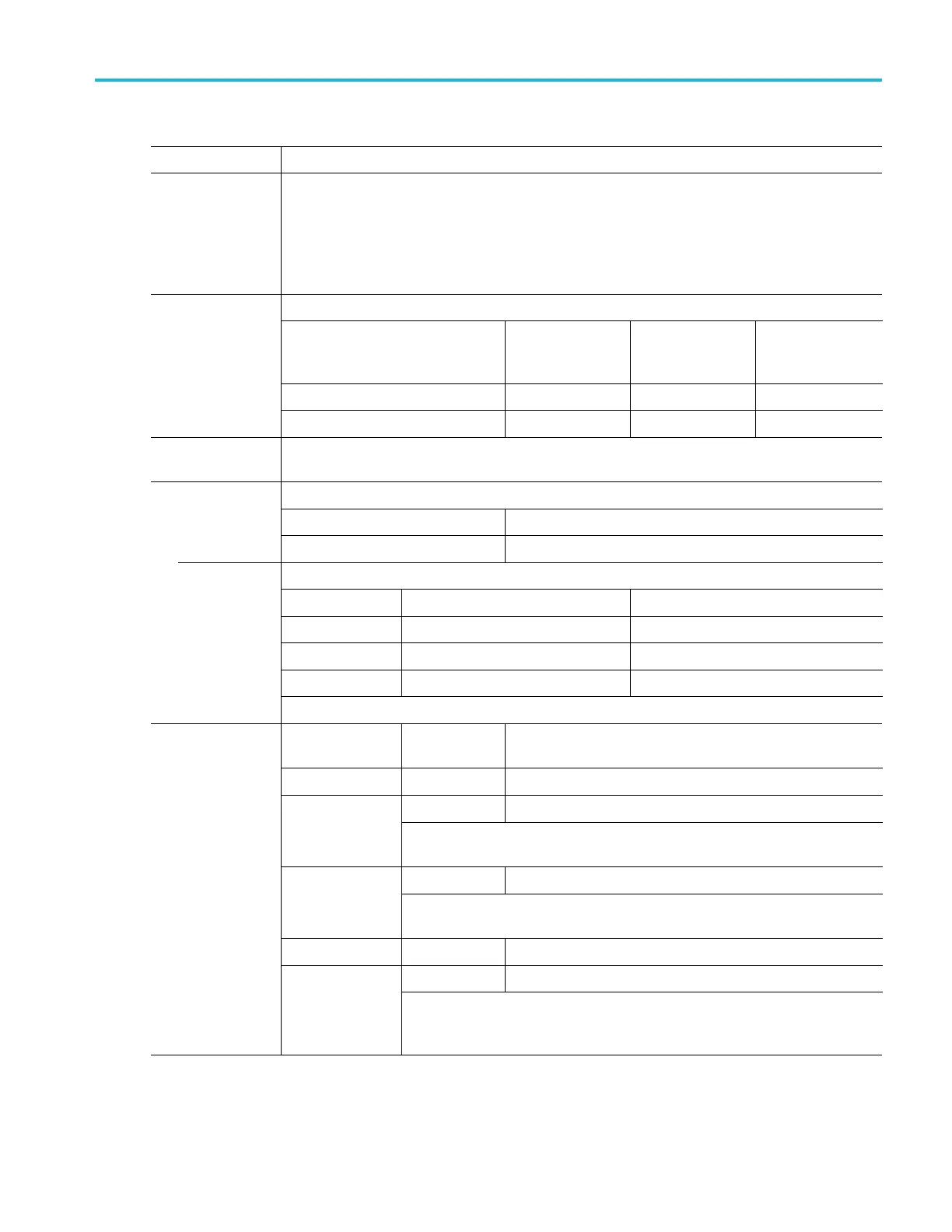

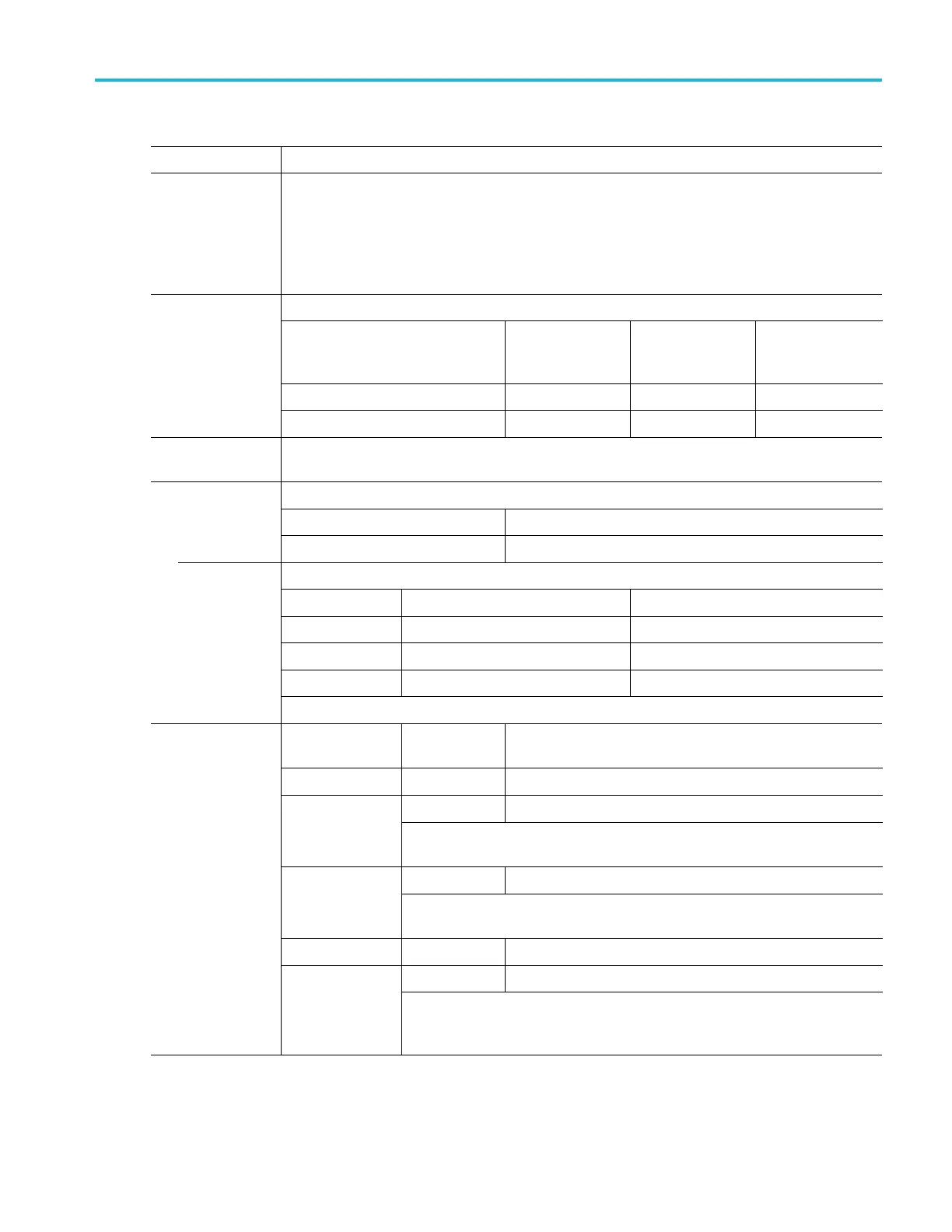

For all vertical settings, the minimums are:

Trigger type Minimum pulse

width

Minimum re-arm

time

Minimum time

between channels

1

Logic Not applicable 2 ns 2 ns

Logic trigger,

minimum logic or

re-arm time, ty p ical

Time Qualified Logic

4ns 2ns 2ns

Setup/hold time

violation trigger

For all vertical settings, the minimum clock pulse widths are:

Clock Active

2

Clock Inactive

2

Minimum clock

pulse widths,

typical

User hold time + 2.5 ns

3

2ns

The lim i ts are as follows;

Feature Min Max

Setup time

4

–0.5 ns 1.024 ms

Hold time

4

1 ns 1.024 ms

Setup + Hold time

4

0.5 ns 2.048 ms

Setup and hold

time ranges

NOTE. Input coupling on clock and data channels must be the same.

Trigger type Minimum pulse

width

Minimum rearm time

Glitch

4ns

2 ns + 5% of glitch width setting

4ns

2 ns + 5% of width upper limit setting

Pulse-width

NOTE. For the pulse-width trigger class, pulse-width refers to the width of the

pulse being measured. The rearm time refers to the time between pulses.

4ns 2nsRunt

NOTE. For the runt trigger class, pulse width refers to the width of the pulse being

measured. The rearm time refers to the time between pulses.

Time-qualified runt

4ns

8.5 ns + 5% of width setting

4ns

8.5 ns + 5% of delta time setting

Minimum pulse

width and

rearm time

Slew rate

NOTE. For the slew rate trigger class, pulse width refers to the delta time being

measured. The rearm time refers to the time it takes the signal to cross the two

trigger thresholds again.

MDO3000 Series S pecifications and Performance Verification 19

Loading...

Loading...