Control Law Computation

A

1

A

2

B

0

B

1

B

2

)2()1()2()1()()(

21210

nUAnUAnEBnEBnEBnU

; e(n)=Vref-Vout

MOVU ACC,@Vref

SUBU ACC,*XAR2++

LSL ACC,#8 ; ACC=e(n) (Q24)

MOVL @VCNTL_DBUFF+4,ACC

ZAPA

; Voltage control law

MOVL XT,@VCNTL_DBUFF+8 ; XT=e(n-2)

QMPYAL P,XT,*XAR7++ ; b2*e(n-2)

MOVDL XT,@VCNTL_DBUFF+6 ; XT=e(n-1), e(n-2)=e(n-1)

QMPYAL P,XT,*XAR7++ ; ACC=b2*e(n-2), P=b1*e(n-1)

MOVDL XT,@VCNTL_DBUFF+4 ; XT=e(n), e(n-1)=e(n)

QMPYAL P,XT,*XAR7++ ; ACC+=b1*e(n-1), P=b0*e(n)

MOVL XT,@VCNTL_DBUFF+2 ; XT=u(n-2)

QMPYAL P,XT,*XAR7++ ; P=a2*u(n-2)

MOVDL XT,@VCNTL_DBUFF ; XT=u(n-1), u(n-2)=u(n-1)

QMPYAL P,XT,*XAR7++ ; ACC=a2*u(n-2)

ADDL ACC,P ; ACC=a2*u(n-2)+a1*u(n-1)

LSL ACC,#(23-VCNTL_QF+8) ; (Q23)

ADDL ACC,ACC ; (Q24)

MOVL @VCNTL_DBUFF,ACC ; ACC=u(n)

; Saturate the result [min,max]

MINL ACC,*XAR7++

MAXL ACC,*XAR7++

; Duty Cycle Modulation

MOVL XT,ACC

QMPYL P,XT,*XAR7++ ;(Q0)

MOV *XAR3++,P

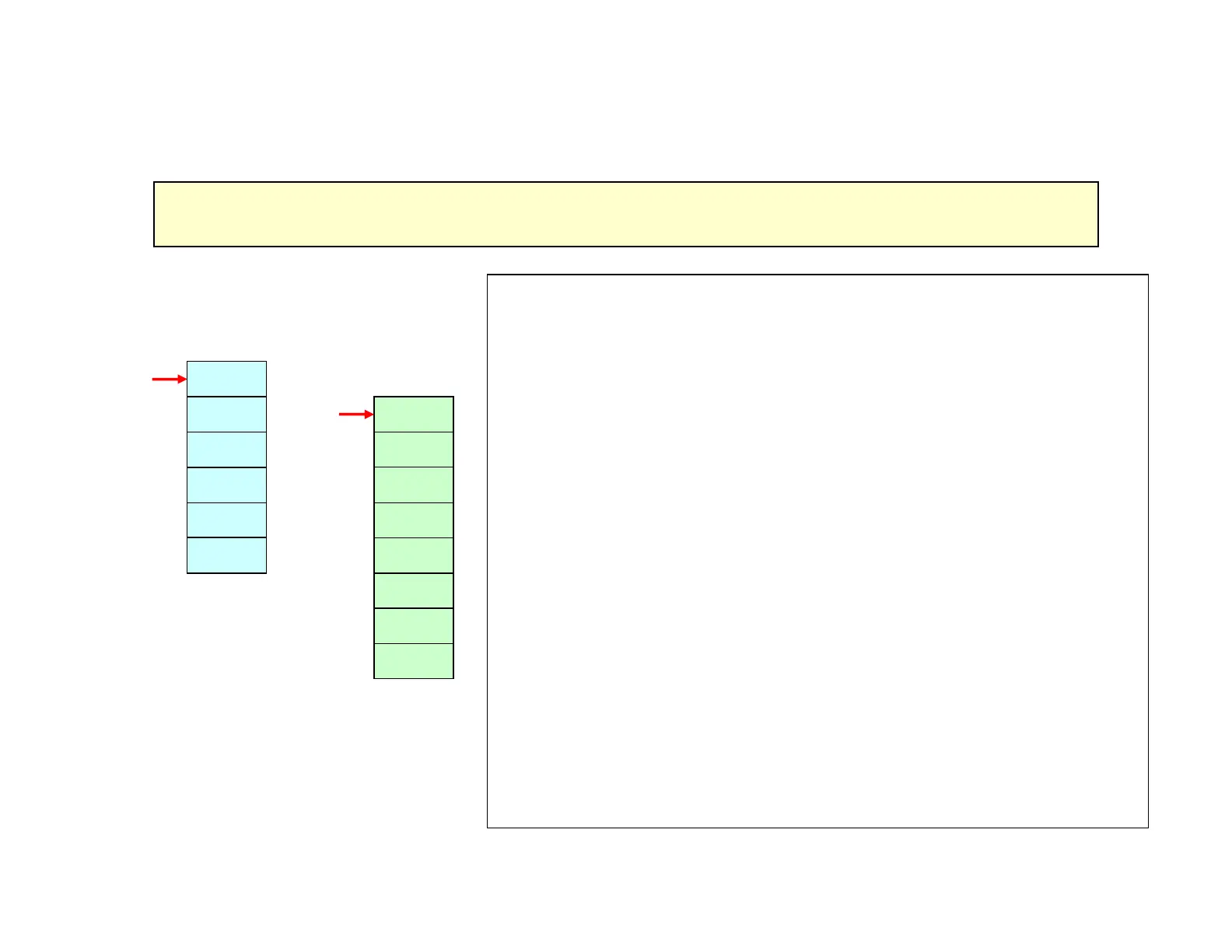

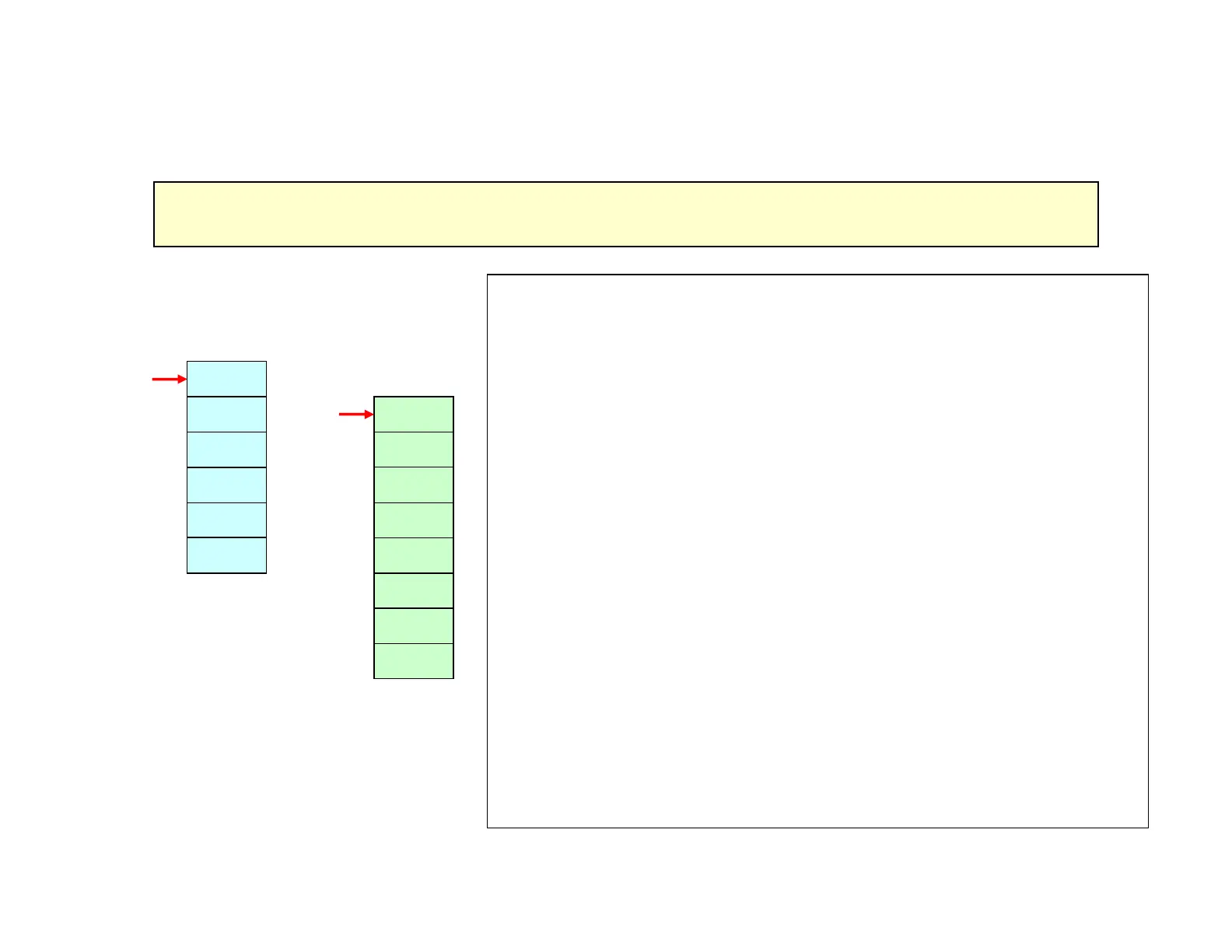

XAR7

min

max

duty

U(n)

U(n-1)

U(n-2)

E(n)

E(n-1)

E(n-2)

DBUFF

Loading...

Loading...